ESD 손상 이해: 유형, 원인 및 부품 신뢰성에 미치는 영향

파괴적 고장, 잠재적 고장, 매개변수 고장 모드

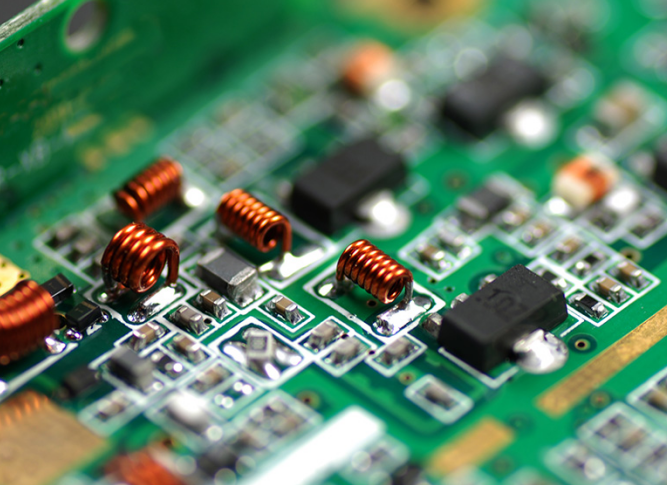

전자 부품의 경우 정전기 방전(ESD)이 부품 신뢰성에 크게 악영향을 미칠 수 있으며, 주로 세 가지 방식으로 나타납니다. 첫 번째는 소위 ‘치명적 결함(catastrophic failures)’으로, 고전압 스파이크에 의해 부품이 즉시 완전히 작동을 멈추는 현상입니다. 두 번째는 숨겨진 ‘잠재적 결함(latent failures)’으로, 초기에는 드러나지 않다가 훨씬 후에야 문제가 발생합니다. 부품은 처음 검사 시 모든 테스트를 통과할 수 있지만, 내부적으로는 시간이 지남에 따라 서서히 열화되기 시작합니다. 이는 병원, 항공기, 자동차 등 중요한 장소에서 기기가 예기치 않게 고장 나게 되는 심각한 문제로 이어질 수 있습니다. 세 번째는 ‘매개변수 결함(parametric failures)’으로, 부품을 완전히 파손시키지는 않지만 전기적 특성을 변화시켜 작동 방식을 바꾸는 결함입니다. 예를 들어 누설 전류가 증가하거나 동작 전압 수준이 달라지는 등의 현상이 점차적으로 부품 성능을 설계 사양보다 저하시키게 됩니다. 2023년 EOS/ESD 협회에서 발표한 최신 자료에 따르면, 반도체 제조 과정에서 발생하는 결함의 약 3분의 1이 ESD 문제로 인해 발생합니다. 특히 고급 집적 회로(IC) 생산 공정에서 이러한 문제가 발생할 경우, 기업은 한 건당 수십만 달러에 달하는 손실을 입을 수 있습니다.

물리적 열화: 게이트 산화막 파열, 유전체 파손, 접합부 손상

현미경으로 물체를 관찰할 때, 정전기 방전은 구조적 문제를 세 가지 주요 방식으로 유발합니다. MOSFET의 경우, 이 현상을 ‘게이트 산화막 파열(gate oxide rupture)’이라고 부릅니다. 기본적으로 방전이 매우 얇은 절연층을 관통하는 것입니다. 기술이 10나노미터보다 작아질수록 이 문제가 더욱 심각해지는데, 왜냐하면 이러한 산화막 두께가 때때로 약 5~10개의 원자 수준에 불과하기 때문입니다. 다음으로 ‘유전체 파괴(dielectric breakdown)’가 있습니다. 이는 커패시터 또는 기타 절연체 내부에 원치 않는 전도성 경로를 형성하는 것을 의미하며, 일반적으로 단락 회로로 이어집니다. 또 다른 문제는 열 응력으로 인한 접합부 손상(junction damage)입니다. 강렬한 열로 인해 실리콘과 금속 부품 사이의 접합부가 녹아서 트랜지스터의 동작 특성이 영구적으로 변하게 됩니다. 이러한 결함 대부분은 흔히 볼 수 있는 인간의 접촉에서 시작됩니다. 예를 들어, 카펫 위를 걷기만 해도 약 1.5킬로볼트(kV)의 정전기가 축적될 수 있습니다. 그 외 원인으로는 부적절한 도구 사용이나 표면을 과도하게 전도성으로 만드는 이물질(먼지 등)이 있습니다. 특정 장치가 얼마나 취약한지는 그 장치의 종류에 크게 좌우됩니다.

- 저전압 IC : 100V 미만에서 고장 발생

- 분리형 다이오드 : 일반적으로 2–5kV까지 견딤

- 고성능 프로세서 : 250V 이하의 정전기 방전으로 손상될 수 있음

정전기 방전(ESD) 보호 전략: 칩 내부 설계에서 시스템 레벨 구현까지

효과적인 ESD 보호를 위해서는 칩 내부에 직접 보호 장치를 통합하면서 동시에 기판 및 시스템 차원에서 이를 강화하는, 조율된 다층 접근 방식이 필요합니다. 이러한 ‘심층 방어’ 전략은 과도 전압 위협을 민감한 회로에 도달하기 전에 차단하도록 보장합니다.

칩 내부 통합 ESD 보호: 다이오드, SCR, 스냅백 소자

칩 내부 보호 구조는 ESD 사건을 핀 단계에서 바로 차단하기 위해 집적 회로(IC)에 직접 제작됩니다. 주요 해결책은 다음과 같습니다:

- 클램프 다이오드 전압이 안전한 한계를 초과하면 일시적인 전류를 전원 레일 또는 그라운드로 분산시킴

- SCR(실리콘 제어 정류기) 고전류 사건 발생 시 제어된 래치업을 통해 저임피던스 도전 경로를 활성화함

- 스냅백 소자 트리거 후 낮은 전압·고전류 상태로 전이되는 NMOS/PMOS 구성을 활용함

이러한 나노초 응답 소자는 파괴 수준의 10% 미만으로 과전압을 제한하여 게이트 산화막 및 접합부 무결성을 보호하는 데 필수적이다. 설계자는 특히 PCIe 6.0, USB4와 같은 고속 인터페이스에서 보호 강도와 기생 커패시턴스 간의 신중한 균형을 맞춰야 하며, 과도한 커패시턴스는 5 Gbps 이상에서 신호 무결성을 왜곡시킬 수 있다.

시스템 수준 ESD 보호: TVS 다이오드, 필터링 및 견고성 확보를 위한 PCB 배치

보드 수준 보호는 반도체의 허용 한계를 초과하는 고에너지 일시적 현상을 관리함으로써 칩 내부 방호 기능을 보완한다. 핵심 구성 요소는 다음과 같다:

- TVS(과도 전압 억제) 다이오드 i/O 커넥터로부터 2 mm 이내에 배치하여 1 ns 이내에 전압을 5 V 이하로 클램프함

- π-필터 페라이트 비드와 디커플링 커패시터를 결합하여 고주파 ESD 잡음(>100 MHz)을 감쇄함

-

PCB 레이아웃 최적화 실천 방법 :

- 연속적이며 저임피던스인 그라운드 플레인(<15 mΩ)

- TVS 소자와 보호 대상 IC 사이의 트레이스 길이 최소화

- 커플링 방지를 위해 아날로그, 디지털, RF 영역을 전략적으로 분리

IEC 61000-4-2 지침에 따라 구현될 경우, 이러한 조치는 시스템 수준 ESD 내성을 4–8 kV까지 향상시킬 수 있다. 가장 견고한 설계에서는 TVS 클램핑과 최적화된 라우팅을 통합하여 예측 가능하고 저임피던스인 방전 경로를 확립함으로써 에너지가 민감한 노드로 유도되지 않도록 한다.

부품 무결성을 위한 정전기 방지 포장 및 취급 절차

웨이퍼 제조에서 최종 사용에 이르기까지 전체 공정 내내 부품을 무결하게 유지하려면 포장 및 취급 방식을 엄격히 관리해야 합니다. 이를 위해 여러 가지 핵심 재료가 사용됩니다. 정전기 소산성 백(bag)은 표면 전하를 제거하는 데 도움을 주는데, 그 저항값은 10^4~10^11 옴(Ω) 범위에 있습니다. 탄소가 첨가된 고분자로 제작된 전도성 트레이(tray)는 잡음 전류를 실제로 전도하여 제거합니다. 또한, 외부 정전기장으로부터 다중 차원의 보호를 제공하는 고급 금속화 용기(metallized container)도 있습니다. 부품을 이동할 때는 특수 부품 홀더(component holder)를 사용해 모든 부품을 고정시켜 운송 중 손상을 방지합니다. 물류 운영에서는 정전기 방전(ESD) 안전 팔레트(ESD safe pallet)를 활용함으로써, 마찰만으로도 정전기가 발생하는 성가신 삼전기 유도 현상(triboelectric effect)을 방지할 수 있습니다.

민감한 부품을 취급할 때 사람들이 따라야 할 핵심 사항으로는, 직원들이 매일 점검되는 손목 밴드를 착용하여 접지되도록 하는 것, 작업 표면 주변에 이온화기를 설치하여 잔여 정전기 전하를 제거하는 것, 그리고 일반적으로 모든 사람이 그 의미를 이해하는 노란 삼각형 경고 표시를 포장재 등 곳곳에 부착하는 것이 있다. 이러한 조치들을 종합적으로 시행하면 정전기 전압 수준을 100볼트 이하로 유지할 수 있다. 업계 연구에 따르면, 이 수준을 유지하면 ‘파라메트릭 드리프트(parametric drift)’라는 현상을 줄일 수 있는데, 이는 은닉된 정전기 방전(ESD) 손상이 발생하고 있음을 알리는 최초의 징후이다. 다양한 제조업 분야에서 보고된 자료에 따르면, 이러한 접근 방식은 해당 문제를 30퍼센트 이상 감소시킬 수 있다.