การเข้าใจความเสียหายจากไฟฟ้าสถิตย์ (ESD): ประเภท สาเหตุ และผลกระทบต่อความน่าเชื่อถือของชิ้นส่วน

โหมดความล้มเหลวแบบหายนะ แบบแฝง และแบบพารามิเตอร์

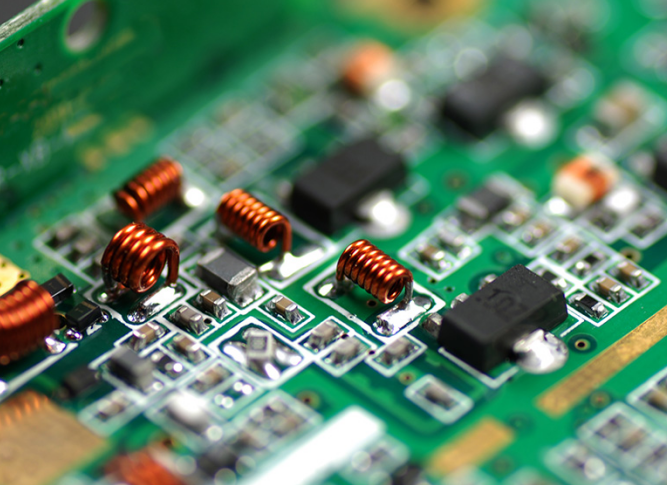

เมื่อพูดถึงอุปกรณ์อิเล็กทรอนิกส์ ปรากฏการณ์การปล่อยประจุไฟฟ้าสถิต (Electrostatic Discharge หรือ ESD) อาจส่งผลกระทบอย่างรุนแรงต่อความน่าเชื่อถือของชิ้นส่วนได้ในสามวิธีหลัก ประการแรกคือความล้มเหลวแบบหายนะ (catastrophic failures) ซึ่งเกิดขึ้นเมื่อชิ้นส่วนหนึ่งถูกโจมตีด้วยคลื่นแรงดันสูงเหล่านั้น แล้วหยุดทำงานทั้งหมดทันที ประการที่สองคือความล้มเหลวแบบแฝง (latent failures) ที่ไม่แสดงอาการออกมาทันที แต่จะปรากฏให้เห็นในภายหลัง ชิ้นส่วนอาจผ่านการทดสอบทั้งหมดได้ในระยะแรก แต่ภายในกลับเริ่มเสื่อมสภาพลงอย่างช้าๆ ตามกาลเวลา ซึ่งจะกลายเป็นปัญหาใหญ่ในอนาคต เมื่ออุปกรณ์ล้มเหลวโดยไม่คาดคิดในสถานที่สำคัญ เช่น โรงพยาบาล เครื่องบิน หรือรถยนต์ ประการที่สามคือความล้มเหลวแบบพารามิเตอร์ (parametric failures) ซึ่งเปลี่ยนแปลงลักษณะการทำงานทางไฟฟ้าของชิ้นส่วน โดยไม่ทำให้ชิ้นส่วนนั้นเสียหายอย่างสมบูรณ์ เช่น กระแสไหลรั่วเพิ่มขึ้น หรือระดับแรงดันไฟฟ้าเปลี่ยนไป ส่งผลให้ประสิทธิภาพของชิ้นส่วนลดลงอย่างค่อยเป็นค่อยไป ตามข้อมูลล่าสุดจากสมาคม EOS/ESD เมื่อปี 2023 พบว่าประมาณหนึ่งในสามของความล้มเหลวทั้งหมดของเซมิคอนดักเตอร์ในระหว่างกระบวนการผลิตเกิดจากปัญหา ESD และเมื่อเหตุการณ์เช่นนี้เกิดขึ้นในการผลิตวงจรรวมขั้นสูง (advanced integrated circuit production) บริษัทอาจสูญเสียเงินหลายแสนดอลลาร์สหรัฐต่อเหตุการณ์หนึ่ง

การเสื่อมสภาพทางกายภาพ: การแตกร้าวของออกไซด์ที่ขั้วควบคุม (Gate Oxide Rupture), การล้มเหลวของไดอิเล็กตริก (Dielectric Breakdown), และความเสียหายต่อรอยต่อ (Junction Damage)

การพิจารณาสิ่งต่าง ๆ ภายใต้กล้องจุลทรรศน์ พบว่าการปล่อยประจุไฟฟ้าสถิตย์ (ESD) ก่อให้เกิดปัญหาเชิงโครงสร้างได้สามวิธีหลัก สำหรับทรานซิสเตอร์แบบ MOSFET ปรากฏการณ์ที่เกิดขึ้นเรียกว่า "การฉีกขาดของชั้นออกไซด์ที่ขั้วควบคุม (gate oxide rupture)" โดยพื้นฐานแล้ว ประจุที่ปล่อยออกมาจะทะลุผ่านชั้นฉนวนที่บางมากเหล่านี้ ซึ่งปัญหานี้ยิ่งรุนแรงขึ้นเมื่อเทคโนโลยีก้าวหน้าไปสู่ขนาดต่ำกว่า 10 นาโนเมตร เนื่องจากความหนาของชั้นออกไซด์เหล่านี้บางครั้งมีเพียงประมาณ 5–10 อะตอมเท่านั้น ประการที่สอง คือ การเสื่อมสภาพของฉนวน (dielectric breakdown) ซึ่งหมายถึงการเกิดทางเดินไฟฟ้าที่ไม่ต้องการภายในตัวเก็บประจุหรือฉนวนชนิดอื่น ๆ ซึ่งโดยทั่วไปนำไปสู่วงจรลัด (short circuits) อีกปัญหาหนึ่งคือ ความเสียหายต่อข้อต่อ (junction damage) ที่เกิดจากความเครียดจากความร้อน ความร้อนอย่างรุนแรงทำให้รอยต่อระหว่างซิลิคอนกับส่วนประกอบโลหะละลาย ส่งผลให้สมรรถนะของทรานซิสเตอร์เปลี่ยนแปลงไปอย่างถาวร ความล้มเหลวส่วนใหญ่เหล่านี้เริ่มต้นจากการสัมผัสของมนุษย์ในชีวิตประจำวัน เช่น การเดินบนพรมอาจทำให้เกิดประจุสะสมได้ประมาณ 1.5 กิโลโวลต์ สาเหตุอื่น ๆ ได้แก่ เครื่องมือที่ไม่เหมาะสม หรือสิ่งสกปรกที่ทำให้พื้นผิวนำไฟฟ้าได้ง่ายเกินไป ระดับความเปราะบางของอุปกรณ์ขึ้นอยู่กับประเภทของอุปกรณ์ที่เรากำลังพูดถึงเป็นหลัก

- ไอซีแอลแรงดันต่ำ : เสียหายที่ <100 โวลต์

- ไดโอดแบบแยกชิ้น : โดยทั่วไปสามารถทนต่อแรงดันได้ 2–5 กิโลโวลต์

- โปรเซสเซอร์ขั้นสูง : อาจเสียหายจากประจุไฟฟ้าสถิตที่ต่ำกว่า 250 โวลต์

กลยุทธ์การป้องกัน ESD: จากการออกแบบในชิปถึงการนำไปปฏิบัติในระดับระบบ

การป้องกัน ESD อย่างมีประสิทธิภาพจำเป็นต้องใช้แนวทางแบบบูรณาการและหลายชั้น โดยรวมมาตรการป้องกันไว้โดยตรงในชิปซิลิคอน พร้อมเสริมความแข็งแกร่งด้วยการป้องกันในระดับแผงวงจรและระดับระบบ กลยุทธ์การป้องกันแบบซ้อนชั้นนี้จะช่วยดักจับภัยคุกคามชั่วคราวก่อนที่จะเข้าถึงวงจรที่ไวต่อการรบกวน

การป้องกัน ESD แบบบูรณาการภายในชิป: ไดโอด ไทริสเตอร์ควบคุม (SCR) และอุปกรณ์แบบ Snapback

โครงสร้างการป้องกันภายในชิปถูกผลิตขึ้นโดยตรงในวงจรรวม เพื่อดักจับเหตุการณ์ ESD ที่ระดับขาของชิป โซลูชันหลักประกอบด้วย:

- ไดโอดหนีบ เบี่ยงเบนกระแสชั่วคราวไปยังรางจ่ายไฟหรือสายกราวด์ เมื่อแรงดันเกินค่าขีดจำกัดที่ปลอดภัย

- SCRs (Silicon Controlled Rectifiers) เปิดใช้งานเส้นทางการนำกระแสแบบความต้านทานต่ำในระหว่างเหตุการณ์ที่มีกระแสสูง โดยผ่านกลไกการล็อก (latch-up) ที่ควบคุมได้

- อุปกรณ์แบบ Snapback ใช้โครงสร้าง NMOS/PMOS ซึ่งเปลี่ยนสถานะไปเป็นโหมดแรงดันต่ำแต่กระแสสูงหลังจากถูกกระตุ้น

องค์ประกอบเหล่านี้ที่ตอบสนองภายในนาโนวินาทีสามารถจำกัดแรงดันเกิน (voltage overshoot) ให้อยู่ต่ำกว่า 10% ของระดับที่ทำลายวงจร — ซึ่งมีความสำคัญอย่างยิ่งต่อการรักษาความสมบูรณ์ของชั้นออกไซด์ที่ขั้วประตู (gate oxides) และข้อต่อ (junctions) ผู้ออกแบบจำเป็นต้องปรับสมดุลระหว่างประสิทธิภาพของการป้องกันกับความจุแฝง (parasitic capacitance) อย่างรอบคอบ โดยเฉพาะในอินเทอร์เฟซความเร็วสูง (เช่น PCIe 6.0, USB4) ซึ่งความจุส่วนเกินอาจทำให้สัญญาณบิดเบือนเมื่อความเร็วสูงกว่า 5 Gbps

การป้องกัน ESD ระดับระบบ: ไดโอด TVS การกรองสัญญาณ และการจัดวางแผงวงจร (PCB Layout) เพื่อความทนทาน

การป้องกันระดับแผงวงจรเสริมการป้องกันภายในชิป โดยจัดการกับกระแสชั่วคราวที่มีพลังงานสูงซึ่งเกินขีดความสามารถในการรองรับของสารกึ่งตัวนำ องค์ประกอบที่จำเป็น ได้แก่:

- ไดโอด TVS (Transient Voltage Suppression) : ติดตั้งไว้ภายในระยะ 2 มม. จากขั้วต่ออินพุต/เอาต์พุต (I/O) เพื่อจำกัดแรงดันให้ต่ำกว่า 5 V ภายในเวลาไม่เกิน 1 นาโนวินาที

- ตัวกรองแบบพาย (Π-filters) : รวมลูกปัดเฟอร์ไรต์ (ferrite beads) กับตัวเก็บประจุแยกสัญญาณ (decoupling capacitors) เพื่อลดเสียงรบกวนจาก ESD ความถี่สูง (>100 MHz)

-

แนวทางปฏิบัติที่ดีที่สุดสำหรับการจัดวางวงจรบนแผงวงจร (PCB layout best practices) :

- ระนาบกราวด์แบบต่อเนื่องที่มีอิมพีแดนซ์ต่ำ (<15 มิลลิโอห์ม)

- ความยาวของสายนำ (trace) ระหว่างอุปกรณ์ TVS กับไอซีที่ได้รับการป้องกันควรสั้นที่สุดเท่าที่จะทำได้

- การแยกส่วนวงจรอะนาล็อก ดิจิทัล และ RF อย่างมีกลยุทธ์ เพื่อป้องกันไม่ให้สัญญาณรบกวนกันผ่านการเหนี่ยวนำ (coupling)

เมื่อดำเนินการตามแนวทางของมาตรฐาน IEC 61000-4-2 มาตรการเหล่านี้สามารถเพิ่มความสามารถในการทนต่อ ESD ระดับระบบ (system-level ESD immunity) ได้ถึง 4–8 kV งานออกแบบที่แข็งแกร่งที่สุดจะรวมการจำกัดแรงดันด้วยอุปกรณ์ TVS เข้ากับการจัดวางเส้นทางสัญญาณ (routing) อย่างเหมาะสม เพื่อสร้างเส้นทางปล่อยพลังงานที่คาดการณ์ได้และมีอิมพีแดนซ์ต่ำ—โดยเบี่ยงเบนพลังงานออกไปจากจุดสำคัญที่ไวต่อการรบกวน

บรรจุภัณฑ์และวิธีการจัดการเพื่อป้องกัน ESD สำหรับรักษาความสมบูรณ์ของชิ้นส่วน

การรักษาส่วนประกอบให้อยู่ในสภาพสมบูรณ์ตลอดกระบวนการทั้งหมด ตั้งแต่การผลิตเวเฟอร์จนถึงการใช้งานขั้นสุดท้าย จำเป็นต้องควบคุมอย่างเข้มงวดเกี่ยวกับวิธีการบรรจุหีบห่อและการจัดการส่วนประกอบเหล่านั้น มีวัสดุหลักหลายชนิดที่ใช้เพื่อวัตถุประสงค์นี้ ถุงป้องกันไฟฟ้าสถิตแบบกระจายประจุ (Static dissipative bags) ช่วยกำจัดประจุผิวหน้า เนื่องจากมีค่าความต้านทานอยู่ระหว่าง 10^4 ถึง 10^11 โอห์ม ถาดนำไฟฟ้า (Conductive trays) ที่ผลิตจากพอลิเมอร์ที่ผสมคาร์บอนสามารถนำกระแสไฟฟ้ารั่วไหลออกไปได้จริง ส่วนภาชนะเคลือบโลหะ (metallized containers) ที่ทันสมัยเหล่านั้นสร้างเกราะป้องกันหลายชั้นจากสนามไฟฟ้าสถิตภายนอก เมื่อมีการเคลื่อนย้ายชิ้นส่วน จะใช้ที่ยึดชิ้นส่วนพิเศษ (special component holders) เพื่อคงตำแหน่งของทุกชิ้นไว้อย่างมั่นคง จึงไม่มีส่วนใดเสียหายระหว่างการขนส่ง นอกจากนี้ การดำเนินงานด้านโลจิสติกส์ยังได้รับประโยชน์จากพาเลทที่ปลอดภัยต่อไฟฟ้าสถิต (ESD safe pallets) ซึ่งช่วยป้องกันปรากฏการณ์ไตรโบอิเล็กทริก (triboelectric effect) อันน่ารำคาญ ซึ่งเป็นปรากฏการณ์ที่ทำให้เกิดไฟฟ้าสถิตสะสมขึ้นเพียงจากการเสียดสีระหว่างวัตถุ

สิ่งสำคัญที่บุคลากรจำเป็นต้องปฏิบัติตามเมื่อจัดการกับชิ้นส่วนที่ไวต่อความเสียหายจากไฟฟ้าสถิตย์ ได้แก่ การตรวจสอบให้แน่ใจว่าพนักงานถูกต่อสายดินอย่างเหมาะสมโดยใช้สายรัดข้อมือ (wrist straps) ซึ่งต้องผ่านการทดสอบทุกวัน การติดตั้งเครื่องกำจัดประจุไฟฟ้าสถิตย์ (ionizers) รอบพื้นผิวโต๊ะทำงานเพื่อกำจัดประจุไฟฟ้าสถิตย์ที่ค้างอยู่ และการติดป้ายเตือนมาตรฐานไว้ทั่วบริเวณ โดยทั่วไปจะเป็นป้ายรูปสามเหลี่ยมสีเหลืองที่ติดอยู่บนบรรจุภัณฑ์ ซึ่งทุกคนรู้ดีว่าหมายถึงอะไร ทั้งหมดนี้ร่วมกันช่วยควบคุมระดับไฟฟ้าสถิตย์ให้อยู่ต่ำกว่า 100 โวลต์ งานวิจัยในอุตสาหกรรมชี้ว่า การรักษาระดับไฟฟ้าสถิตย์ไว้ที่ค่านี้จะช่วยลดปรากฏการณ์ที่เรียกว่า "การเปลี่ยนแปลงของพารามิเตอร์ (parametric drift)" ซึ่งเป็นสัญญาณแรกที่บ่งชี้ว่าอาจเกิดความเสียหายจาก ESD แบบแฝงอยู่ รายงานต่าง ๆ จากภาคการผลิตระบุว่า แนวทางนี้สามารถลดปัญหาดังกล่าวได้มากกว่า 30 เปอร์เซ็นต์