Inzicht in ESD-schade: soorten, oorzaken en impact op de betrouwbaarheid van componenten

Catastrofale, latente en parametrische storingsmodi

Wanneer het op elektronica aankomt, kan elektrostatische ontlading (ESD) de betrouwbaarheid van componenten op drie belangrijke manieren ernstig verstoren. Ten eerste zijn er zogenaamde catastrofale storingen, waarbij een component wordt getroffen door een hoge-spanningspiek en onmiddellijk volledig uitvalt. Vervolgens zijn er de sluwe latente storingen die pas veel later zichtbaar worden. Componenten kunnen bij eerste inspectie alle tests met vlag en wimpel halen, maar binnenin beginnen ze langzaam in de loop van de tijd te verslechteren. Dit wordt later een groot probleem wanneer apparaten onverwacht uitvallen op cruciale plaatsen zoals ziekenhuizen, vliegtuigen of auto’s. Het derde type is parametrische storingen, waardoor de elektrische werking van componenten verandert zonder dat ze daadwerkelijk defect raken. Denk hierbij aan hogere lekstromen of afwijkende spanningsniveaus die geleidelijk leiden tot een slechtere prestatie dan normaal. Volgens recente cijfers van de EOS/ESD Association uit 2023 wordt ongeveer een derde van alle halfgeleiderstoringen tijdens de productie veroorzaakt door ESD-problemen. En wanneer dit zich voordoet bij de productie van geavanceerde geïntegreerde schakelingen, kunnen bedrijven per incident honderdduizenden dollars verliezen.

Fysieke verslechtering: Poortoxide-ruptuur, diëlektrische doorbraak en junctieschade

Als we dingen onder een microscoop bekijken, veroorzaakt elektrostatische ontlading structurele problemen op drie hoofdmanieren. Bij MOSFET’s treedt wat ‘gate-oxidebreuk’ wordt genoemd. In feite boort de ontlading zich door die uiterst dunne isolatielagen heen. Dit wordt een groter probleem naarmate de technologie kleiner wordt dan 10 nanometer, omdat deze oxide-lagen soms slechts zo’n 5 tot 10 atomen dik zijn. Vervolgens hebben we diëlektrische doorbraak, wat in feite betekent dat er ongewenste geleidende paden worden gevormd binnen condensatoren of andere isolatoren, meestal resulterend in kortsluitingen. Een ander probleem is junctieschade als gevolg van thermische belasting. De intense hitte smelt de verbindingen tussen silicium- en metalen onderdelen, waardoor de werking van transistors permanent verandert. De meeste van deze storingen beginnen met gewoon, alledaags menselijk contact. Alleen al lopen op een tapijt kan ongeveer 1,5 kilovolt lading opbouwen. Andere oorzaken zijn ongeschikte gereedschappen of vuil dat oppervlakken te goed elektrisch geleidend maakt. De kwetsbaarheid van een component hangt sterk af van het soort apparaat waarover we het hebben.

- Laagspannings-IC's : Vallen uit bij <100 V

- Discrete diodes : Houden doorgaans 2–5 kV stand

- Geavanceerde processors : Kunnen worden beschadigd door ontladingen onder de 250 V

ESD-beschermingsstrategieën: van op-chipontwerp tot systeemniveau-implementatie

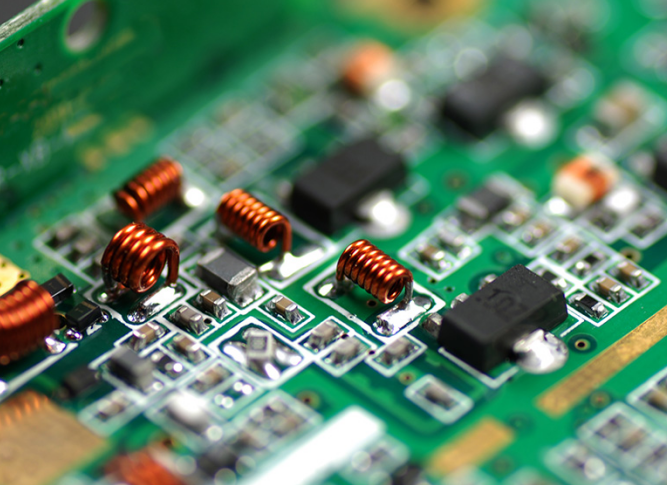

Effectieve ESD-bescherming vereist een gecoördineerde, meervoudige aanpak — waarbij beveiligingsmaatregelen direct in de siliciumchip worden geïntegreerd en op het printplaten- en systeemniveau worden versterkt. Deze 'defense-in-depth'-strategie zorgt ervoor dat transiënte bedreigingen worden opgevangen voordat ze gevoelige schakelingen bereiken.

Geïntegreerde op-chip ESD-bescherming: diodes, SCRs en snapback-apparaten

Op-chipbeschermingsstructuren worden direct in geïntegreerde schakelingen gefabriceerd om ESD-gebeurtenissen op pinniveau op te vangen. Belangrijke oplossingen zijn:

- Clampdiodes leid tijdelijke stromen af naar voedingsspanningslijnen of aarde zodra de spanning veilige drempels overschrijdt

- SCR's (Silicon Controlled Rectifiers) activeer laag-impedantie geleidingspaden tijdens gebeurtenissen met hoge stroom via gecontroleerde latch-up

- Snapback-apparaten benut NMOS/PMOS-configuraties die na activering overgaan naar lage-spannings-, hoge-stroomtoestanden

Deze elementen met nanoseconde-reactietijd beperken de spanningsoverschrijding tot minder dan 10% van destructieve niveaus — essentieel voor het behoud van gateoxiden en junctie-integriteit. Ontwerpers moeten zorgvuldig een evenwicht vinden tussen beschermingssterkte en parasitaire capaciteit, met name bij high-speed interfaces (bijv. PCIe 6.0, USB4), waarbij te veel capaciteit de signaalintegriteit boven 5 Gbps kan verstoren.

ESD-bescherming op systeemniveau: TVS-diodes, filtering en printplaatlayout voor robuustheid

Printplaatniveau-bescherming vormt een aanvulling op chipgebonden bescherming door transiënten met hogere energie te beheren die de toleranties van halfgeleiders overschrijden. Essentiële elementen zijn:

- TVS (Transient Voltage Suppression)-diodes : Geplaatst binnen 2 mm van I/O-connectoren om spanningen onder de 5 V aan te klemmen in minder dan 1 ns

- π-filters : Combineren ferrietkralen en ontkoppelcondensatoren om hoogfrequent ESD-geluid (>100 MHz) te dempen

-

Aanbevolen praktijken voor PCB-layout :

- Ononderbroken, laag-impedantie aardvlakken (<15 mΩ)

- Minimale trace-lengte tussen TVS-apparaten en beschermd IC's

- Strategische scheiding van analoge, digitale en RF-secties om koppeling te voorkomen

Wanneer deze maatregelen worden toegepast conform de richtlijnen van IEC 61000-4-2, kan de ESD-immuniteit op systeemniveau met 4–8 kV worden verbeterd. De meest robuuste ontwerpen integreren TVS-aanklemming met geoptimaliseerde routing om voorspelbare, laag-impedantie afvoerpaden te vormen — waardoor energie wordt afgeleid van gevoelige knooppunten.

ESD-beschermende verpakking en behandeling voor onderdeelintegriteit

Het behouden van componenten in perfecte staat gedurende het gehele proces, van wafelfabricatie tot het uiteindelijke gebruik, vereist strenge controle over de manier waarop ze worden verpakt en gehandhaafd. Er worden verschillende belangrijke materialen voor dit doel gebruikt. Antistatische zakken helpen oppervlakteladingen te elimineren, omdat ze een weerstand hebben tussen 10^4 en 10^11 ohm. Geleidende trays, vervaardigd uit koolstofversterkte polymeren, geleiden eventuele ongewenste elektrische stromen af. En dan zijn er nog die geavanceerde gemetalliseerde containers die meervoudige lagen bescherming bieden tegen externe elektrostatische velden. Bij het verplaatsen van onderdelen zorgen speciale componentenhouders ervoor dat alles op zijn plaats blijft, zodat niets tijdens het transport beschadigd raakt. Ook logistieke operaties profiteren van ESD-veilige pallets, die het vervelende tribo-elektrisch effect voorkomen — waarbij statische elektriciteit ontstaat door wrijving tussen materialen.

De belangrijkste maatregelen die mensen moeten naleven bij het omgaan met gevoelige componenten, zijn onder andere ervoor zorgen dat medewerkers geaard zijn met behulp van polsbandjes die dagelijks worden getest, ionisatoren plaatsen rond werkoppervlakken om eventuele resterende statische lading te neutraliseren en standaard waarschuwingstekens overal aanbrengen – meestal gele driehoeken op verpakkingen, waarvan iedereen het betekenis kent. Samen zorgt deze opstelling ervoor dat de statische elektriciteit onder de 100 volt blijft. Onderzoek in de industrie toont aan dat het handhaven van dit niveau parametrische drift verminderd, wat in feite het eerste teken is van mogelijke verborgen ESD-schade. Volgens diverse rapporten uit de productiesector kan deze aanpak dergelijke problemen met meer dan 30 procent verminderen.