Pag-unawa sa Pinsala Dulot ng ESD: Mga Uri, Dahilan, at Epekto sa Katiyakan ng mga Komponente

Mga Mode ng Pagkabigo: Katastropiko, Nakatago, at Parametrik

Kapag tumutukoy sa mga elektroniko, ang electrostatic discharge o ESD ay maaaring talagang makasira sa katiyakan ng mga bahagi sa tatlong pangunahing paraan. Una ay ang tinatawag nating mga nakamamatay na pagkabigo—kung saan ang isang bahagi ay nahihit ng mga mataas na voltage spike at biglang nawawalan ng kakayahang gumana nang ganap. Pangalawa ay ang mga palihim na pagkabigo na hindi agad lumilitaw kundi maraming panahon pa ang lumipas. Maaaring pumasa ang mga bahagi sa lahat ng pagsusulit sa unang tingin, ngunit sa loob nila ay unti-unting nadadeteriorate habang tumatagal ang panahon. Ito ay naging malaking problema sa hinaharap kapag nabigo ang mga device nang hindi inaasahan sa mahahalagang lugar tulad ng mga ospital, eroplano, o sasakyan. Ang ikatlo ay ang mga parametric na pagkabigo—na nagbabago sa paraan kung paano gumagana ang mga bahagi sa elektrikal nang hindi talaga binabasag ang mga ito. Isipin ang mga bagay tulad ng mas mataas na leakage currents o iba’t ibang antas ng voltage na unti-unting nagpapababa sa pagganap ng mga bahagi kaysa sa dapat nilang gawin. Ayon sa kamakailang datos mula sa EOS/ESD Association noong 2023, halos isang ikatlo ng lahat ng mga pagkabigo ng semiconductor sa panahon ng pagmamanupaktura ay dulot ng mga problema sa ESD. At kapag ito’y nangyayari sa produksyon ng advanced integrated circuit, maaaring mawala ng sampu-sampung libong dolyar ang mga kumpanya bawat insidente.

Pisikal na Pagkabulok: Pagsabog ng Gate Oxide, Pagkabigo ng Dielectric, at Pinsala sa Junction

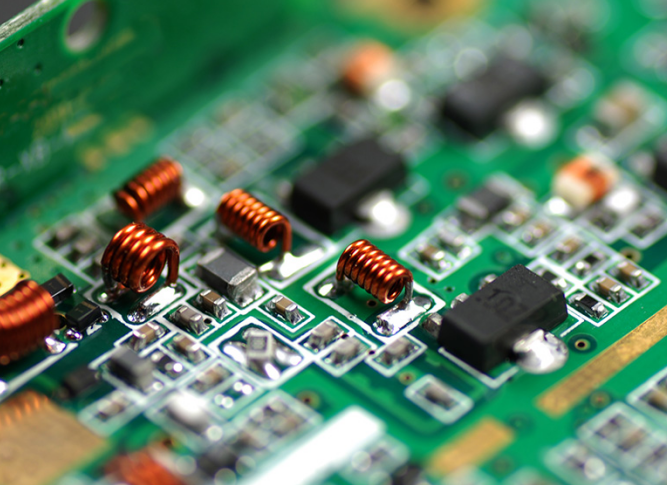

Kapag tinitingnan ang mga bagay sa ilalim ng mikroskopyo, ang electrostatic discharge (ESD) ay nagdudulot ng mga problema sa istruktura sa tatlong pangunahing paraan. Sa kaso ng mga MOSFET, ang nangyayari ay tinatawag na gate oxide rupture (pagkabasag ng oxide layer sa gate). Sa madaling salita, ang discharge ay tumutusok sa mga napakapino na layer ng insulasyon. Lumalaki ang problema na ito habang ang teknolohiya ay sumisikip nang higit sa 10 nanometro dahil ang mga oxide layer na ito ay minsan ay may kapal na humihigit sa lima hanggang sampung atom lamang. Mayroon ding dielectric breakdown (pagkabigkis ng dielectric), na nangangahulugan ng pagbuo ng di-nais na mga daanan ng kuryente sa loob ng mga capacitor o iba pang insulator, na karaniwang nagreresulta sa short circuit. Isa pa ring isyu ang junction damage (pinsala sa sambungan) na dulot ng init na stress. Ang matinding init ay natutunaw ang mga koneksyon sa pagitan ng silicon at mga bahagi ng metal, na nagpapabago ng paraan kung paano gumagana ang mga transistor nang pamanahon. Karamihan sa mga kabiguan na ito ay nagsisimula sa karaniwang pisikal na pakikipag-ugnayan ng tao. Ang simpleng paglalakad sa carpet ay maaaring magdulot ng humigit-kumulang 1.5 kilovolts na singil. Kasama rin sa iba pang sanhi ang hindi angkop na mga kasangkapan o alikabok na nagpapagawa ng mga ibabaw na masyadong madaling magpadala ng kuryente. Ang antas ng kahinaan ng isang bagay ay nakasalalay nang husto sa uri ng device na pinag-uusapan.

- Mababang-voltage na IC : Nabibigo sa <100 V

- Mga hiwalay na diode : Karaniwang kayang tiisin ang 2–5 kV

- Mga advanced na processor : Maaaring masira dahil sa mga discharge sa ilalim ng 250 V

Mga Estratehiya sa Proteksyon laban sa ESD: Mula sa On-Chip na Disenyo hanggang sa Implementasyon sa System-Level

Ang epektibong proteksyon laban sa ESD ay nangangailangan ng isang koordinadong, maraming antas na pamamaraan—na pagsasama-sama ng mga pananggalang direktang sa loob ng silicon habang pinapalakas ang mga ito sa antas ng board at system. Ang estratehiyang ito na 'defense-in-depth' ay nagpapatiyak na ang mga transient na banta ay hinaharang na bago pa man dumating sa sensitibong circuitry.

Nakaintegrado na On-Chip na Proteksyon laban sa ESD: Mga Diode, SCR, at Snapback Device

Ang mga istrukturang on-chip na proteksyon ay ginagawa nang direkta sa loob ng mga integrated circuit upang harangin ang mga ESD event sa antas ng pin. Kasama sa mga pangunahing solusyon:

- Clamp Diodes magpahatid ng mga pansamantalang kasalukuyang daloy patungo sa mga power rail o ground kapag ang boltahe ay lumampas sa mga ligtas na antas

- SCRs (Silicon Controlled Rectifiers) aktibahin ang mga landas ng pagdaloy na may mababang impekdansya sa panahon ng mga kaganapan na may mataas na kasalukuyan gamit ang kontroladong latch-up

- Mga device na may epekto ng snapback gumamit ng mga konpigurasyon ng NMOS/PMOS na nagbabago sa mga estado na may mas mababang boltahe at mataas na kasalukuyan pagkatapos ma-trigger

Ang mga elemento na may tugon sa loob ng nanosegundo na ito ay limitado ang voltage overshoot sa hindi hihigit sa 10% ng mga antas na nakapipinsala—na napakahalaga upang mapanatili ang integridad ng gate oxides at junction. Kailangan ng mga designer na maingat na balansehin ang lakas ng proteksyon laban sa parasitic capacitance, lalo na sa mga high-speed interface (halimbawa: PCIe 6.0, USB4), kung saan ang labis na capacitance ay maaaring magdulot ng distorsyon sa signal integrity sa taas ng 5 Gbps.

Sistemang Proteksyon Laban sa ESD: Mga TVS Diode, Pag-filter, at Layout ng PCB para sa Kagandahan ng Pagganap

Ang proteksyon sa antas ng board ay sumusuplemento sa mga pangsilicon na depensa sa pamamagitan ng pagmamanage ng mga transients na may mas mataas na enerhiya na lumalampas sa mga toleransiya ng semiconductor. Ang mga pangunahing elemento ay kinabibilangan ng:

- Mga TVS (Transient Voltage Suppression) diode : Ipinapalagay sa loob ng 2 mm mula sa mga konektor ng I/O upang i-clamp ang mga voltage sa ibaba ng 5 V sa loob ng kahit isang nanosekundo (ns)

- mga π-filter : Pinagsasama ang mga ferrite bead at mga decoupling capacitor upang bawasan ang ESD noise na may mataas na frequency (>100 MHz)

-

Mga pinakamahusay na gawi sa pagpaplano ng PCB :

- Patuloy na lupa na may mababang impedance (<15 mΩ)

- Pinakamaliit na haba ng trace sa pagitan ng mga device na TVS at ng mga IC na protektado

- Estratehikong paghihiwalay ng mga seksyon na analog, digital, at RF upang maiwasan ang coupling

Kapag isinasagawa ayon sa mga gabay ng IEC 61000-4-2, ang mga hakbang na ito ay maaaring itaas ang immunity ng sistema laban sa ESD ng 4–8 kV. Ang pinakamatibay na mga disenyo ay pinalalakas ang TVS clamping kasama ang optimisadong routing upang magtatag ng mga predictable at mababang impedance na discharge path—upang patnubayan ang enerhiya palayo sa mga sensitibong node.

Pangangalaga at Pakete na Protektibo Laban sa ESD para sa Integridad ng Komponent

Ang pagpapanatili ng mga komponente na buo sa buong proseso—mula sa paggawa ng wafer hanggang sa panghuling paggamit—ay nangangailangan ng mahigpit na kontrol sa paraan ng kanilang pagpapakete at paghawak. May ilang pangunahing materyales na ginagamit para sa layuning ito. Ang mga static dissipative bag ay tumutulong sa pag-alis ng mga surface charge dahil may resistance levels sila na nasa pagitan ng 10^4 at 10^11 ohms. Ang mga conductive tray na gawa sa carbon-loaded polymers ay talagang nagdadala palabas ng anumang stray electrical currents. At mayroon ding mga sopistikadong metallized container na gumagawa ng maraming layer ng proteksyon laban sa mga panlabas na electrostatic field. Kapag inililipat ang mga bahagi, ang mga espesyal na component holder ang nagpapanatili ng lahat sa tamang posisyon upang walang anuman ang nasasaktan habang nakakalipat. Ang mga operasyon sa logistics ay kumikinabang din mula sa ESD safe pallets na nagpipigil sa nakakainis na triboelectric effect—kung saan ang mga bagay ay nagkakaroon ng static electricity simpleng dahil sa pagrub sa isa’t isa.

Ang mga pangunahing bagay na kailangang sundin ng mga tao kapag hinahawakan ang mga sensitibong komponent ay kasama ang pagtiyak na ang mga miyembro ng tauhan ay nakakonekta sa lupa gamit ang mga wrist strap na sinusubok araw-araw, ang paglalagay ng mga ionizer sa paligid ng mga ibabaw ng trabaho upang alisin ang anumang natitirang static charge, at ang paglagay ng mga karaniwang babala sa lahat ng lugar—karaniwang mga dilaw na tatsulok sa mga kahon na agad na nauunawaan ng lahat ng tao ang kahulugan. Bukod dito, ang buong setup na ito ay panatag na pinapanatili ang antas ng static electricity sa ilalim ng 100 volts. Ayon sa pananaliksik sa industriya, ang pagpapanatili nito sa antas na ito ay nababawasan ang isang bagay na tinatawag na parametric drift, na sa pangkalahatan ay ang unang palatandaan na maaaring may nakatagong ESD damage na nangyayari. Ayon sa iba’t ibang ulat mula sa mga sektor ng pagmamanupaktura, ang ganitong pamamaraan ay maaaring bawasan ang mga ganitong uri ng isyu ng higit sa 30 porsyento.