Разбиране на повредите от електростатично разреждане (ESD): видове, причини и въздействие върху надеждността на компонентите

Катастрофални, скрити и параметрични режими на отказ

Когато става дума за електроника, електростатичният разряд или ESD може сериозно да повлияе върху надеждността на компонентите по три основни начина. Първият от тях са така наречените катастрофални повреди, при които някой компонент е ударен от високоволтови импулси и изведнъж напълно спира да функционира. Вторият тип са скритите (латентни) повреди, които не се проявяват веднага, а много по-късно. Компонентите може да издържат всички тестове при първоначална проверка, но вътрешно започват бавно да се деградират с течение на времето. Това става сериозен проблем в бъдеще, когато устройствата изведнъж се повредят в критични среди като болници, самолети или автомобили. Третият тип са параметричните повреди, които променят електрическото поведение на компонентите, без всъщност да ги повредят физически. Става дума например за по-високи токове на подтичане или за промени в нивата на напрежение, които постепенно намаляват производителността на компонентите спрямо техните спецификации. Според последните данни от асоциацията EOS/ESD от 2023 г. около една трета от всички повреди на полупроводникови устройства по време на производството се дължат на проблеми, свързани с ESD. А когато това се случи при производството на напреднали интегрални схеми, компаниите могат да загубят стотици хиляди долара при всеки отделен случай.

Физическо разрушаване: пробив на оксидния затвор, пробив на диелектрика и повреда на прехода

Разглеждайки нещата под микроскоп, електростатичният разряд предизвиква структурни проблеми по три основни начина. Когато става дума за MOSFET-ове, настъпващото явление се нарича пробив на гейт-оксидния слой. По същество разрядът пробива тези изключително тънки изолационни слоеве. Този проблем става по-сериозен с напредването на технологиите към размери под 10 нанометра, тъй като тези оксидни слоеве понякога са дебели само около 5–10 атома. Следва пробив на диелектрика, който по същество означава създаването на нежелани проводими пътища в кондензатори или други изолатори, обикновено водещи до късо съединение. Друг проблем е повреждането на преходите поради термичен стрес. Интензивното топлинно въздействие разтопява връзките между кремниевите и металните компоненти, което необратимо променя начина, по който работят транзисторите. Повечето от тези откази започват с обикновения човешки контакт. Само ходенето по килим може да натрупа около 1,5 киловолта заряд. Други причини включват некачествени инструменти или мръсотия, която прави повърхностите прекалено проводими. Степента на уязвимост зависи значително от типа устройство, за което става дума.

- Интегрални схеми за ниско напрежение : Отказват при <100 V

- Дискретни диоди : Обикновено издръжат 2–5 kV

- Напреднали процесори : Могат да бъдат повредени от разряди под 250 V

Стратегии за защита срещу електростатично разреждане (ESD): От проектиране на чиповете до системно ниво

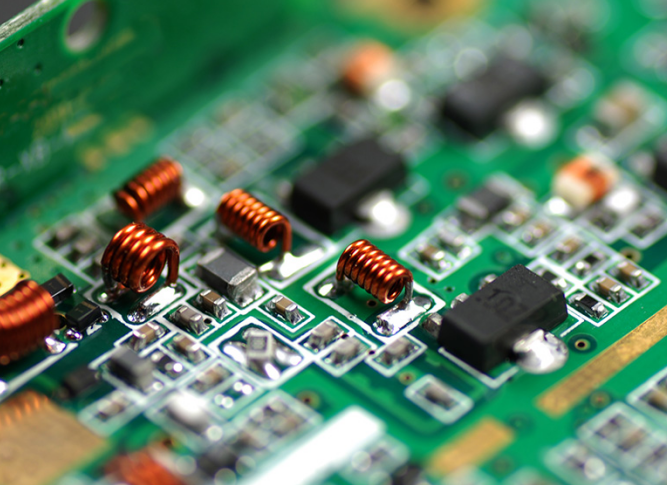

Ефективната защита срещу ESD изисква координиран, многослойен подход — интегриране на предпазни мерки направо в кремния, като се усилват допълнително на ниво печатна платка и система. Тази стратегия за защита на дълбочина гарантира, че преходните заплахи ще бъдат пресечени, преди да достигнат чувствителните вериги.

Интегрирана на чипа защита срещу ESD: Диоди, тиристори (SCR) и устройства с ефект на затваряне (snapback)

Структурите за защита на чипа се изготвят директно в интегралните схеми, за да пресичат събитията на ESD на ниво контакт. Основните решения включват:

- Зажимни диоди да отвеждат преходни токове към захранващите шини или земя, след като напрежението надхвърли безопасните граници

- SCR (кремниеви управляеми изправители) активират пътища с ниско съпротивление за провеждане по време на събития с висок ток чрез контролирано заключване

- Устройства с ефект 'snapback' използват конфигурации NMOS/PMOS, които преминават в състояния с по-ниско напрежение и висок ток след активиране

Тези елементи с отговорен период в наносекунди ограничават превишението на напрежението до по-малко от 10 % от разрушителните стойности — което е критично за запазване цялостта на гейт-оксидните слоеве и преходите. Проектиращите инженери трябва внимателно да балансират силата на защитата спрямо паразитната капацитетност, особено при високочестотни интерфейси (напр. PCIe 6.0, USB4), където излишната капацитетност може да наруши целостта на сигнала при честоти над 5 Гбит/с.

Системна защита срещу електростатично разреждане (ESD): диоди TVS, филтриране и подредба на печатната платка за повишена надеждност

Защитата на ниво печатна платка допълва защитните механизми в чипа, като управлява преходни процеси с по-висока енергия, които надхвърлят допустимите стойности за полупроводниковите компоненти. Основни елементи включват:

- Диоди TVS (за потискане на преходни напрежения) поставени на разстояние до 2 мм от входно-изходните (I/O) конектори, за да ограничават напреженията под 5 V за по-малко от 1 нс

- пи-филтри комбинират феритни перли и декуплиращи кондензатори, за да потиснат високочестотен ЕСР шум (>100 MHz)

-

Най-добрите практики за трасиране на печатни платки (PCB) :

- Непрекъснати земни площи с ниско съпротивление (<15 mΩ)

- Минимална дължина на проводниците между устройствата TVS и защитените ИС

- Стратегическо разделяне на аналоговите, цифровите и ВЧ секции, за да се предотврати взаимното им влияние

Ако се прилагат според насоките на IEC 61000-4-2, тези мерки могат да повишат устойчивостта на системата към електростатично разреждане (ЕСР) с 4–8 kV. Най-издръжливите проекти интегрират ограничаване чрез TVS устройства заедно с оптимизирано трасиране, за да се осигурят предвидими и с ниско съпротивление пътища за разреждане — като насочват енергията далеч от чувствителни възли.

Опаковка и процедури за защита от ЕСР за запазване цялостта на компонентите

Запазването на компонентите непокътнати през целия процес — от производството на пластинки (wafer) до крайното им използване — изисква строг контрол върху начина, по който се опаковат и обработват. За тази цел се използват няколко ключови материала. Статично дисипативните пликчета помагат за отстраняване на повърхностните заряди, тъй като имат съпротивление в диапазона от 10^4 до 10^11 ома. Проводящите подложки, изработени от полимери, натоварени с въглерод, действително отвеждат всеки случайно възникнал електрически ток. А метализираните контейнери с многослойна конструкция осигуряват защита срещу външни електростатични полета. При преместването на компоненти специалните държачи гарантират, че всичко остава на мястото си, така че нищо да не бъде повредено по време на транспортиране. Логистичните операции също печелят от използването на ESD-безопасни палети, които предотвратяват раздразняващия трибоелектричен ефект — явление, при което статичен електрически заряд се натрупва просто поради триене между повърхности.

Основните неща, които хората трябва да спазват при работа с чувствителни компоненти, включват осигуряване на заземяване на персонала чрез предписани за целта киткови ленти, които се тестват всеки ден, разполагане на йонизатори около работните повърхности, за да се елиминира остатъчният статичен заряд, и поставяне на стандартни предупредителни знаци навсякъде – обикновено жълти триъгълници върху опаковките, чието значение е добре известно на всички. Тази комплексна система поддържа нивото на статично електричество под 100 волта. Проучванията в отрасъла показват, че поддържането на това ниво намалява така нареченото параметрично отклонение, което е основният индикатор за възможни скрити повреди вследствие на електростатично разреждане (ESD). Според различни доклади от производствените сектори този подход може да намали подобни проблеми с повече от 30 процента.

Съдържание

- Разбиране на повредите от електростатично разреждане (ESD): видове, причини и въздействие върху надеждността на компонентите

- Стратегии за защита срещу електростатично разреждане (ESD): От проектиране на чиповете до системно ниво

- Опаковка и процедури за защита от ЕСР за запазване цялостта на компонентите