Comprensión de los daños por ESD: Tipos, causas e impacto en la fiabilidad de los componentes

Modos de fallo catastrófico, latente y paramétrico

Cuando se trata de electrónica, la descarga electrostática (ESD) puede afectar gravemente la fiabilidad de los componentes de tres maneras principales. En primer lugar, están las denominadas averías catastróficas, en las que un componente recibe una sobretensión y deja de funcionar por completo de inmediato. A continuación, existen las sutiles averías latentes, que no se manifiestan hasta mucho después: los componentes pueden superar todas las pruebas a primera vista, pero internamente comienzan a degradarse lentamente con el tiempo. Esto se convierte en un problema importante a largo plazo, cuando los dispositivos fallan de forma inesperada en entornos críticos, como hospitales, aviones o automóviles. El tercer tipo son las averías paramétricas, que alteran el comportamiento eléctrico de los componentes sin llegar a dañarlos físicamente; por ejemplo, corrientes de fuga más elevadas o niveles de tensión diferentes, que hacen que los componentes desempeñen progresivamente peor su función de lo previsto. Según datos recientes de la Asociación EOS/ESD publicados en 2023, aproximadamente un tercio de todas las averías de semiconductores durante la fabricación se deben a problemas de ESD. Y cuando esto ocurre en la producción de circuitos integrados avanzados, las empresas pueden llegar a perder cientos de miles de dólares por cada incidente.

Degradación física: rotura del óxido de compuerta, ruptura dieléctrica y daño en la unión

Al observar las cosas bajo un microscopio, la descarga electrostática provoca problemas estructurales de tres maneras principales. En el caso de los MOSFET, lo que ocurre se denomina rotura del óxido de puerta. Básicamente, la descarga perfora esas capas aislantes extremadamente finas. Este problema se agrava a medida que la tecnología avanza hacia escalas inferiores a los 10 nanómetros, ya que dichas capas de óxido tienen, en ocasiones, un grosor de tan solo unos 5 a 10 átomos. Luego está la ruptura dieléctrica, que consiste, fundamentalmente, en la creación de trayectorias conductoras no deseadas dentro de condensadores u otros materiales aislantes, lo que normalmente conduce a cortocircuitos. Otra incidencia es el daño en las uniones causado por tensiones térmicas: el calor intenso funde las conexiones entre las partes de silicio y metal, alterando de forma irreversible el funcionamiento de los transistores. La mayoría de estos fallos comienza con un contacto humano habitual: simplemente caminar sobre una alfombra puede acumular alrededor de 1,5 kilovoltios de carga. Otros factores responsables incluyen herramientas inadecuadas o suciedad que hace que las superficies conduzcan la electricidad con demasiada facilidad. El grado de vulnerabilidad de un componente depende en gran medida del tipo de dispositivo del que se trate.

- Circuitos integrados de baja tensión : Fallan a <100 V

- Diodos discretos : Normalmente soportan 2–5 kV

- Procesadores avanzados : Pueden dañarse por descargas inferiores a 250 V

Estrategias de protección contra descargas electrostáticas (ESD): desde el diseño en chip hasta la implementación a nivel de sistema

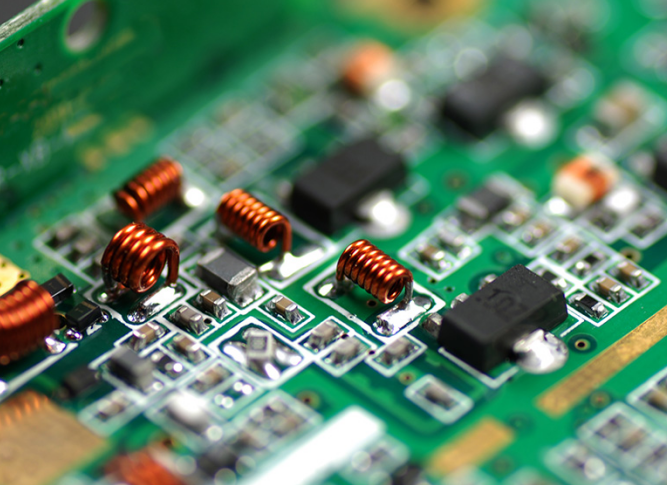

Una protección eficaz contra ESD requiere un enfoque coordinado y multicapa, que integre medidas de seguridad directamente en el silicio y las refuerce a nivel de placa y de sistema. Esta estrategia de defensa en profundidad garantiza que las sobretensiones transitorias sean interceptadas antes de alcanzar los circuitos sensibles.

Protección integrada contra ESD en chip: diodos, SCR y dispositivos de disparo (snapback)

Las estructuras de protección en chip se fabrican directamente en los circuitos integrados para interceptar los eventos de ESD a nivel de terminal. Las soluciones clave incluyen:

- Diodos de protección desvía las corrientes transitorias hacia las pistas de alimentación o a tierra una vez que el voltaje supera los umbrales seguros

- SCR (Rectificadores Controlados de Silicio) activan trayectorias de conducción de baja impedancia durante eventos de alta corriente mediante un bloqueo controlado

- Dispositivos de retroceso rápido (snapback) aprovechan configuraciones NMOS/PMOS que pasan a estados de bajo voltaje y alta corriente tras la activación

Estos elementos de respuesta en nanosegundos limitan la sobretensión a menos del 10 % de los niveles destructivos, lo cual es fundamental para preservar la integridad de las capas de óxido de puerta y de las uniones. Los diseñadores deben equilibrar cuidadosamente la capacidad de protección frente a la capacitancia parásita, especialmente en interfaces de alta velocidad (por ejemplo, PCIe 6.0, USB4), donde una capacitancia excesiva puede distorsionar la integridad de la señal por encima de 5 Gbps.

Protección contra ESD a nivel de sistema: Diodos TVS, filtrado y disposición de PCB para robustez

La protección a nivel de placa complementa las defensas integradas en el chip al gestionar transitorios de mayor energía que superan las tolerancias de los semiconductores. Los elementos esenciales incluyen:

- Diodos TVS (supresión transitoria de voltaje) : Colocado a menos de 2 mm de los conectores de entrada/salida (I/O) para limitar las tensiones por debajo de 5 V en menos de 1 ns

- filtros Π : Combinan cuentas de ferrita y condensadores de desacoplamiento para atenuar el ruido electrostático de alta frecuencia (>100 MHz)

-

Buenas prácticas en el diseño de la disposición de componentes en la placa de circuito impreso (PCB) :

- Planos de tierra continuos y de baja impedancia (<15 mΩ)

- Longitud mínima de pista entre los dispositivos TVS y los circuitos integrados protegidos

- Separación estratégica de las secciones analógica, digital y de radiofrecuencia (RF) para evitar acoplamientos no deseados

Cuando se implementan conforme a las directrices de la norma IEC 61000-4-2, estas medidas pueden elevar la inmunidad del sistema frente a descargas electrostáticas (ESD) en 4–8 kV. Los diseños más robustos integran la limitación mediante dispositivos TVS con un trazado optimizado, estableciendo trayectorias de descarga predecibles y de baja impedancia que desvían la energía lejos de los nodos sensibles.

Embalaje y manipulación protectores contra ESD para garantizar la integridad de los componentes

Mantener los componentes intactos durante todo el proceso, desde la fabricación de obleas hasta su uso final, requiere un control estricto sobre cómo se empaquetan y manipulan. Para ello se utilizan varios materiales clave. Las bolsas disipativas de estática ayudan a eliminar las cargas superficiales, ya que presentan niveles de resistencia entre 10^4 y 10^11 ohmios. Las bandejas conductoras fabricadas con polímeros cargados con carbono conducen efectivamente cualquier corriente eléctrica residual. Y luego están esos sofisticados contenedores metalizados que crean múltiples capas de protección contra campos electrostáticos externos. Al transportar componentes, soportes especiales para componentes mantienen todo en su lugar para evitar daños durante el traslado. Asimismo, las operaciones logísticas se benefician de palets seguros frente a descargas electrostáticas (ESD), que previenen ese molesto efecto triboeléctrico mediante el cual los materiales acumulan electricidad estática simplemente por rozamiento.

Las medidas clave que las personas deben seguir al manipular componentes sensibles incluyen, por ejemplo, asegurarse de que el personal esté conectado a tierra mediante pulseras antiestáticas que se someten a prueba diariamente, colocar ionizadores alrededor de las superficies de trabajo para eliminar cualquier carga electrostática residual y fijar letreros de advertencia estándar en todas partes —normalmente triángulos amarillos en los embalajes, cuyo significado resulta familiar para todos—. En conjunto, esta configuración mantiene los niveles de electricidad estática por debajo de 100 voltios. Las investigaciones industriales demuestran que mantener dicho nivel reduce un fenómeno denominado «deriva paramétrica», que constituye básicamente la primera señal de que podría estar ocurriendo daño oculto por descargas electrostáticas (ESD). Según diversos informes del sector manufacturero, este enfoque puede reducir dichos problemas en más del 30 %.

Tabla de Contenido

- Comprensión de los daños por ESD: Tipos, causas e impacto en la fiabilidad de los componentes

- Estrategias de protección contra descargas electrostáticas (ESD): desde el diseño en chip hasta la implementación a nivel de sistema

- Embalaje y manipulación protectores contra ESD para garantizar la integridad de los componentes