ESD損傷の理解:種類、原因、および部品信頼性への影響

破滅的障害、潜在的障害、パラメトリック障害モード

電子機器において、静電気放電(ESD)は、部品の信頼性に大きく影響を与える可能性があり、主に3つの形で問題を引き起こします。まず1つ目は「破壊的故障」で、高電圧スパイクが部品に直接作用し、即座に完全に機能しなくなる状態です。次に2つ目は、一見すると問題がないように見えても、実際には内部で徐々に劣化が進行し、その後になってようやく顕在化する「潜在的故障」です。このような部品は初期検査ではすべての試験を通過するかもしれませんが、時間とともに内部で劣化が進み、病院・航空機・自動車など、信頼性が極めて重要な場所で、後になって予期せぬ故障を引き起こすという重大な問題につながります。3つ目は「パラメトリック故障」で、部品そのものを物理的に破損させることなく、電気的特性(たとえば漏れ電流の増加や動作電圧の変化など)を変化させ、結果として性能を徐々に低下させるものです。2023年にEOS/ESD協会が発表した最新の統計によると、製造工程中の半導体の故障の約3分の1がESDによるものとされています。また、このような事象が高度集積回路(IC)の製造工程で発生した場合、企業は1件あたり数十万ドルもの損失を被る可能性があります。

物理的劣化:ゲート酸化膜の破壊、誘電体の破壊、接合部の損傷

顕微鏡で物事を見ると、静電気放電(ESD)は構造的な問題を引き起こす主に3つの方法があります。MOSFETの場合、起こる現象は「ゲート酸化膜破壊」と呼ばれます。基本的には、放電が極めて薄い絶縁層を貫通してしまうのです。この問題は、技術が10ナノメートル未満の微細化へと進むにつれてより深刻化します。なぜなら、これらの酸化膜は場合によってはわずか5~10個の原子厚さしかないからです。次に、「誘電体破壊」があります。これは、コンデンサーやその他の絶縁体内部に意図しない導電経路を形成することを意味し、通常は短絡を引き起こします。さらに、「接合部損傷」という問題もあります。これは、放電による急激な熱ストレスによって、シリコンと金属部品の間の接合部が溶融し、トランジスタの動作特性を永久に変化させてしまうものです。こうした故障のほとんどは、日常的な人間の接触から始まります。たとえば、カーペットの上を歩くだけでも約1.5キロボルトの静電荷が蓄積されることがあります。その他の原因には、不適切な工具の使用や、表面を過剰に導電性にするほこりなどの異物も挙げられます。対象となるデバイスの静電気に対する脆弱性は、そのデバイスの種類によって大きく異なります。

- 低電圧IC :100 V未満で故障

- ディスクリートダイオード :通常、2–5 kVまで耐える

- 高度なプロセッサ :250 V未満の放電によって損傷を受ける可能性あり

静電気放電(ESD)保護戦略:チップ内設計からシステムレベル実装まで

効果的なESD保護には、チップ内への直接組み込みと基板・システムレベルでの補強を統合した、調整された多層構造のアプローチが必要です。この「深さ方向の防御(Defense-in-Depth)」戦略により、過渡的な脅威が感度の高い回路に到達する前に遮断されます。

チップ内統合型ESD保護:ダイオード、SCR、スナップバックデバイス

チップ内保護構造は、集積回路(IC)に直接形成され、ピンレベルでESD事象を遮断します。主な解決策には以下が含まれます:

- クランプダイオード 電圧が安全なしきい値を超えた際に、一時的な電流を電源レールまたはグランドへ分流する

- SCR(シリコン制御整流子) 高電流事象発生時に、制御されたラッチアップにより低インピーダンスの導通経路を活性化する

- スナップバック素子 トリガー後に低電圧・高電流状態へ移行するNMOS/PMOS構成を活用する

これらのナノ秒応答素子は、破壊レベルに対する電圧オーバーシュートを10%未満に抑制する——ゲート酸化膜および接合部の信頼性確保にとって極めて重要である。設計者は、特にPCIe 6.0やUSB4などの高速インタフェースにおいて、保護性能と寄生容量とのバランスを慎重に検討しなければならない。なぜなら、過剰な容量は5 Gbpsを超える信号整合性を損なう可能性があるからである。

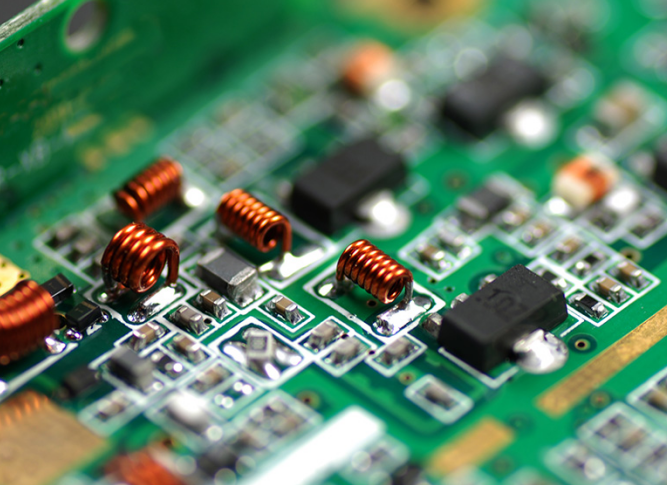

システムレベルESD保護:TVSダイオード、フィルタリング、および堅牢性を実現するPCBレイアウト

基板レベルの保護は、半導体の許容範囲を超える高エネルギー瞬時過電圧を管理することで、チップ内保護機能を補完する。その主要要素には以下が含まれる:

- TVS(過渡電圧サプレッション)ダイオード i/Oコネクタから2 mm以内に配置し、1 ns未満で電圧を5 V以下にクランプする

- π型フィルタ フェライトビーズとデカップリングコンデンサを組み合わせて、高周波ESDノイズ(>100 MHz)を減衰させる

-

PCBレイアウトにおけるベストプラクティス :

- 連続的かつ低インピーダンスのグラウンドプレーン(<15 mΩ)

- TVSデバイスと保護対象IC間のトレース長を最小限に抑える

- アナログ、デジタル、RFセクションを戦略的に分離し、相互結合を防止する

IEC 61000-4-2ガイドラインに従って実装された場合、これらの対策により、システムレベルのESD耐性を4~8 kV向上させることができます。最も堅牢な設計では、TVSクランプと最適化された配線を統合し、予測可能かつ低インピーダンスの放電パスを確立することで、エネルギーを感度の高いノードから遠ざけます。

部品の品質保全のためのESD保護包装および取扱い

ウエハー製造から最終使用に至るまでの全工程において、部品を無傷のまま保つには、包装および取扱い方法を厳密に管理する必要があります。この目的で使用される主な材料にはいくつかあります。静電気帯電防止袋(スタティック・ディシペーティブ・バッグ)は、表面電荷を除去するために、抵抗値が10^4~10^11オームの範囲となるよう設計されています。カーボン充填ポリマーで作られた導電性トレイは、不要な静電気電流を実際に導電して逃がします。さらに、外部の静電界から多重の保護層を提供する高機能メタライズド容器もあります。部品を搬送する際には、特殊な部品ホルダーを使用してすべての部品を固定し、輸送中の損傷を防ぎます。また、ロジスティクス業務では、摩擦起電効果(接触・摩擦によって静電気が発生する現象)を防止するESD対応パレットが活用され、こうした不快な静電気の蓄積を未然に防ぎます。

感度の高い部品を扱う際に従うべき主なポイントには、スタッフが毎日検査されるリストストラップを用いてアース接続されることを確認すること、作業台周辺にイオナイザーを設置して残留静電気を除去すること、および標準的な警告標識(一般に、誰もがその意味を理解する黄色の三角形のマーク)をあらゆる場所に掲示することが含まれます。これらの対策を総合的に実施することで、静電気レベルを100ボルト未満に抑制できます。業界の研究によると、このレベルを維持することで「パラメトリック・ドリフト」と呼ばれる現象が低減されます。これは、潜在的な静電気放電(ESD)による損傷が発生している可能性を示す最初の兆候です。製造業界からの各種報告によれば、このようなアプローチにより、該当する問題を30%以上削減できるとされています。