Az ESD-károk megértése: típusok, okok és hatásuk az alkatrészek megbízhatóságára

Katasztrofális, rejtett és paraméteres hibamódok

Amikor az elektronikáról van szó, az elektrosztatikus kisülés (ESD) komolyan befolyásolhatja az alkatrészek megbízhatóságát három fő módon. Először is vannak a katasztrofális hibák, amikor egy alkatrész olyan magasfeszültségű csúcsoknak van kitéve, és azonnal teljesen működésképtelenné válik. Másodszor pedig ott vannak ezek a rejtett, latens hibák, amelyek csak jóval később jelentkeznek. Az alkatrészek első ránézésre talán átmennek minden teszten, de belül lassan, fokozatosan romlanak. Ez később nagy problémát okozhat, amikor az eszközök váratlanul meghibásodnak fontos helyeken, például kórházakban, repülőgépekben vagy autókban. A harmadik típus a parametrikus hibák, amelyek megváltoztatják az alkatrészek elektromos működését anélkül, hogy ténylegesen meghibásodnának. Ilyenek például a növekedett szivárgási áramok vagy eltérő feszültségszintek, amelyek fokozatosan rosszabbá teszik az alkatrészek teljesítményét, mint amilyennek lenniük kellene. A 2023-ban az EOS/ESD Szövetség által közölt legfrissebb adatok szerint az összes félvezető-hiba körülbelül egyharmada gyártás közben ESD-problémákból ered. Amikor ez előfordul fejlett integrált áramkörök gyártása során, a cégek egyetlen esetben is több százezer dollárt veszíthetnek.

Fizikai degradáció: kapuoxid-rövidzár, dielektromos átütés és átmenet-károsodás

Ha mikroszkóp alatt vizsgáljuk a dolgokat, az elektrosztatikus kisülés három fő módon okoz szerkezeti problémákat. A MOSFET-ek esetében ezt kapuoxid-rövidzárnak nevezik. Alapvetően a kisülés átütési hatást gyakorol azokon a rendkívül vékony szigetelőrétegeken. Ez egyre súlyosabb problémává válik, ahogy a technológia 10 nanométernél kisebb méretűvé válik, mivel ezek az oxidrétegek néha mindössze 5–10 atom vastagságúak. Ezt követi a dielektromos átütés, amely lényegében nem kívánt vezető pályák kialakulását jelenti kondenzátorok vagy más szigetelőanyagok belsejében, általában rövidzárat eredményezve. Egy másik probléma a hőterhelés által okozott átmenetkárosodás. Az intenzív hő felolvadja a szilícium és a fém alkatrészek közötti kapcsolatokat, és végleg megváltoztatja a tranzisztorok működését. Ezek közül a hibák többsége egyszerű emberi érintéssel kezdődik. Csak egy szőnyegen való sétálás is körülbelül 1,5 kilovolt töltést képes felhalmozni. Más okok közé tartoznak a rossz minőségű eszközök vagy a szennyeződés, amelyek túlságosan jól vezetővé teszik a felületeket. Egy adott eszköz érzékenysége nagymértékben függ attól, hogy milyen típusú eszközről van szó.

- Alacsony feszültségű IC-k : Hibás működés <100 V-nál

- Diszkrét diódák : Általában 2–5 kV-ot bírnak el

- Fejlett processzorok : Károsodhatnak 250 V-nál alacsonyabb feszültségű kisülésektől

ESD-védelemi stratégiák: A chipre integrált tervezéstől a rendszerszintű megvalósításig

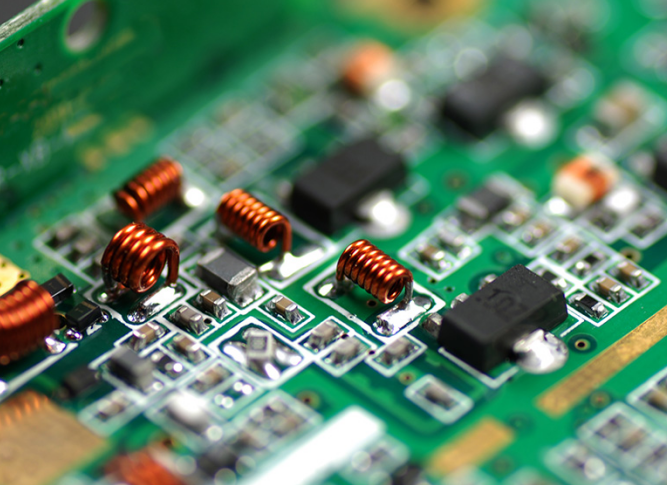

Az hatékony ESD-védelem koordinált, többrétegű megközelítést igényel – a védelmi mechanizmusokat közvetlenül a szilíciumba építik be, miközben egyidejűleg megerősítik őket a nyomtatott áramkörös lap és a rendszer szintjén is. Ez a mélységi védelem stratégia biztosítja, hogy az átmeneti fenyegetések a kritikus áramkörökhöz érkezésük előtt le legyenek állítva.

Integrált, chipre épített ESD-védelem: Diódák, tirisztorok (SCR) és snapback-eszközök

A chipre épített védőstruktúrákat közvetlenül az integrált áramkörökbe gyártják, hogy az ESD-eseményeket a csatlakozópont szintjén észleljék és leállítsák. Fő megoldások:

- Kapcsolódiódák átirányítja a tranziens áramokat a tápfeszültség-sínre vagy földre, ha a feszültség meghaladja a biztonságos küszöbértékeket

- SCR-ek (szilíciumvezérelt egyenirányítók) alacsony impedanciájú vezetési utakat aktiválnak nagyáramú események során vezérelt záródással

- Snapback-eszközök nMOS/PMOS-konfigurációkat használnak, amelyek kiváltás után alacsonyabb feszültségű, nagyáramú állapotba váltanak

Ezek a nanoszekundumos válaszidejű elemek a feszültség-túllendülést kevesebb mint 10%-ra korlátozzák a pusztító szintekhez képest – ez elengedhetetlen a kapuoxidok és az átmeneti rétegek épségének megőrzéséhez. A tervezőknek gondosan egyensúlyozniuk kell a védőképesség erősségét a parazita kapacitás ellen, különösen a nagysebességű interfészeknél (pl. PCIe 6.0, USB4), ahol a felesleges kapacitás torzíthatja a jelminőséget 5 Gbps felett.

Rendszerszintű ESD-védelem: TVS-diódák, szűrés és nyomtatott áramköri lap (PCB) elrendezés a megbízhatóság érdekében

A nyomtatott áramköri lap szintjén alkalmazott védelem kiegészíti a chipen belüli védelmi mechanizmusokat, mivel kezeli azokat a magasabb energiájú tranziens jeleket, amelyek túllépik a félvezetők tűréshatárait. Alapvető elemei:

- TVS (tranziens feszültségcsillapító) diódák : Az I/O-csatlakozókhoz 2 mm-en belül helyezve, hogy az átfeszültséget 1 ns alatt 5 V alá korlátozza

- π-szűrők : A ferritgyöngyök és a lepárló kondenzátorok kombinációjával csökkentik a nagyfrekvenciás ESD-zavarokat (>100 MHz)

-

PCB-elrendezés legjobb gyakorlatai :

- Folyamatos, alacsony impedanciájú földelési síkok (<15 mΩ)

- Minimális vezeték hossz a TVS-eszközök és a védett IC-k között

- Az analóg, digitális és RF szekciók stratégiai elkülönítése a csatolás megelőzése érdekében

Amennyiben az IEC 61000-4-2 irányelvek szerint valósítják meg, ezek a intézkedések 4–8 kV-tal növelhetik a rendszer szintű ESD-ellenállást. A legszilárdabb tervek a TVS-feszültségkorlátozást optimalizált útvonaltervezéssel egyesítik, hogy megbízható, alacsony impedanciájú levezetési utakat hozzanak létre – így az energiát a kritikus csomópontoktól eltérítik.

ESD-védő csomagolás és kezelés az alkatrészek integritásának biztosítására

A komponensek sértetlenségének megőrzése az egész folyamat során – a szilíciumlemez gyártásától egészen a végfelhasználásig – szigorú ellenőrzést igényel a csomagolásuk és kezelésük tekintetében. Ennek eléréséhez több kulcsfontosságú anyagot használnak. A statikus feltöltődés elleni, szóró hatású tasakok segítenek eltávolítani a felületi töltéseket, mivel ellenállásuk 10^4 és 10^11 ohm között van. A szénbetöltött polimerekkel készült vezetőképes tálcák ténylegesen elvezetik a véletlenül keletkező elektromos áramokat. Ezenkívül léteznek az úgynevezett fémesített tartályok, amelyek többrétegű védelmet nyújtanak a külső elektrosztatikus mezők ellen. Alkatrészek szállítása során speciális alkatrész-tartók biztosítják, hogy minden elem a helyén maradjon, és semmi se sérüljön a szállítás közben. A logisztikai műveletek számára az ESD-biztonságos paletták is előnyös megoldást jelentenek, mivel megakadályozzák azt a zavaró triboelektromos hatást, amely akkor jön létre, amikor a testek egyszerűen egymáshoz dörzsölődnek, és így statikus elektromosságot halmoznak fel.

A kritikus fontosságú irányelvek, amelyeket a személyzetnek be kell tartania az érzékeny alkatrészek kezelésekor, például a munkavállalók földelése speciális csuklópántokkal, amelyeket minden nap ellenőrizni kell, ionizátorok elhelyezése a munkafelületek körül a maradék statikus töltés semlegesítésére, valamint a szokásos figyelmeztető táblák mindenütt történő elhelyezése – általában azok a sárga háromszögek a csomagoláson, amelyeket mindenki ismer és értelmez. Ezen intézkedések együttesen biztosítják, hogy a statikus elektromosság szintje 100 voltnál alacsonyabb maradjon. Az iparági kutatások azt mutatják, hogy e szint fenntartása csökkenti a paraméteres drift jelenségét, amely gyakorlatilag az első jele annak, hogy rejtett ESD-károsodás történhet. Különféle gyártási szektorokból származó jelentések szerint ez a megközelítés ilyen problémák esetében több mint 30 százalékkal csökkentheti az előfordulást.