Zrozumienie uszkodzeń spowodowanych przez ESD: typy, przyczyny oraz wpływ na niezawodność komponentów

Katastrofalne, ukryte i parametryczne tryby awarii

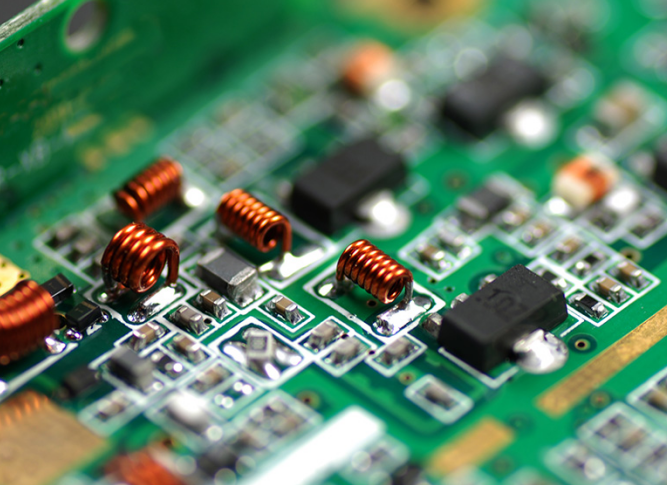

Gdy chodzi o elektronikę, wyładowania elektrostatyczne (ESD) mogą poważnie zakłócać niezawodność komponentów na trzy główne sposoby. Po pierwsze występują tzw. awarie katastrofalne, w których element zostaje uderzony przez wysokonapięciowe impulsy i natychmiast przestaje działać całkowicie. Następnie mamy do czynienia z ukrytymi awariami latentnymi, które nie ujawniają się dopóki nie minie dłuższy czas. Komponenty mogą przejść wszystkie testy przy pierwszym sprawdzeniu, ale wewnętrznie zaczynają się stopniowo degradować. Stanowi to poważny problem w późniejszym okresie, gdy urządzenia niespodziewanie ulegają awarii w miejscach o kluczowym znaczeniu, takich jak szpitale, samoloty czy samochody. Trzecim typem są awarie parametryczne, które zmieniają sposób działania elementów pod względem elektrycznym, nie powodując ich fizycznego uszkodzenia. Przykładem mogą być większe prądy upływu lub odmienne poziomy napięcia, które stopniowo pogarszają wydajność komponentów poniżej założonych wartości. Zgodnie z najnowszymi danymi stowarzyszenia EOS/ESD z 2023 roku około jedna trzecia wszystkich awarii układów półprzewodnikowych podczas produkcji jest spowodowana problemami z ESD. Gdy takie zdarzenie wystąpi w procesie produkcji zaawansowanych układów scalonych, firmy mogą ponieść straty rzędu setek tysięcy dolarów za każde takie zdarzenie.

Degradacja fizyczna: przebicie warstwy tlenku bramkowego, przebicie dielektryka i uszkodzenie złącza

Patrząc na rzeczy pod mikroskopem, wyładowania elektrostatyczne powodują problemy strukturalne w trzech głównych obszarach. W przypadku tranzystorów MOSFET występuje zjawisko nazywane przebiciem warstwy tlenku bramkowego. Zasadniczo wyładowanie przebija te nadzwyczaj cienkie warstwy izolacyjne. Problem ten staje się jeszcze bardziej istotny wraz z miniaturyzacją technologii poniżej 10 nanometrów, ponieważ takie warstwy tlenkowe mają czasem grubość zaledwie 5–10 atomów. Kolejnym zjawiskiem jest przebicie dielektryka, czyli tworzenie niepożądanych ścieżek przewodzących w kondensatorach lub innych materiałach izolacyjnych, co zwykle prowadzi do zwarcia. Trzecim problemem jest uszkodzenie złączy spowodowane naprężeniem termicznym: intensywne nagrzanie topi połączenia między elementami krzemowymi i metalowymi, co trwale zmienia sposób działania tranzystorów. Większość tych awarii rozpoczyna się od zwykłego kontaktu człowieka z urządzeniem. Samo chodzenie po dywanie może wytworzyć ładunek o wartości około 1,5 kV. Innymi czynnikami sprzyjającymi powstawaniu wyładowań są nieodpowiednie narzędzia lub brud, który zbyt łatwo sprawia, że powierzchnie stają się przewodzące. Stopień wrażliwości danego urządzenia zależy w dużej mierze od jego typu.

- Układy scalone niskonapięciowe : ulegają uszkodzeniu przy napięciu < 100 V

- Diody dyskretne : zazwyczaj wytrzymują 2–5 kV

- Zaawansowane procesory : mogą ulec uszkodzeniu w wyniku wyładowań o napięciu poniżej 250 V

Strategie ochrony przed wyładowaniami elektrostatycznymi (ESD): od projektowania ochrony w układzie scalonym po realizację na poziomie systemu

Skuteczna ochrona przed wyładowaniami elektrostatycznymi wymaga skoordynowanego, wielowarstwowego podejścia — obejmującego wdrożenie zabezpieczeń bezpośrednio w krzemie oraz ich wzmocnienie na poziomie płytki i całego systemu. Ta strategia zabezpieczenia głębokiego zapewnia przechwytywanie przebiegów przejściowych jeszcze przed dotarciem ich do wrażliwych obwodów.

Zintegrowana ochrona przed ESD w układzie scalonym: diody, tyristory sterowane (SCR) oraz układy typu snapback

Struktury ochronne w układzie scalonym są wytwarzane bezpośrednio w obwodach scalonych w celu przechwytywania zdarzeń ESD na poziomie styków. Do kluczowych rozwiązań należą:

- Dioda zaciskowa przekierowuje chwilowe prądy do szyn zasilania lub masy, gdy napięcie przekracza bezpieczne progi

- SCR (wyrzutniki krzemowe) aktywuje ścieżki przewodzenia o niskiej impedancji podczas zdarzeń wysokoprądowych poprzez kontrolowane załączanie (latch-up)

- Urządzenia typu snapback korzysta z konfiguracji NMOS/PMOS, które po wyzwoleniu przechodzą w stany o niższym napięciu i wyższym prądzie

Te elementy o czasie odpowiedzi rzędu nanosekund ograniczają przekroczenie napięcia do mniej niż 10% poziomów niszczących — co jest kluczowe dla ochrony tlenków bramek i integralności złączy. Projektanci muszą starannie dobrać siłę ochrony w stosunku do pojemności pasożytniczej, szczególnie w interfejsach wysokiej szybkości (np. PCIe 6.0, USB4), gdzie nadmiar pojemności może zakłócać integralność sygnału przy częstotliwościach powyżej 5 Gbps.

Ochrona systemowa przed ESD: diody TVS, filtry oraz projektowanie płytki PCB zapewniające odporność

Ochrona na poziomie płytki uzupełnia zabezpieczenia wbudowane w układ scalony, zarządzając przebiegami przejściowymi o wyższej energii, przekraczającymi dopuszczalne granice tolerancji półprzewodników. Do podstawowych elementów należą:

- Diody TVS (Transient Voltage Suppression) : Umieszczony w odległości do 2 mm od złączy wejścia/wyjścia (I/O), aby ograniczać napięcia poniżej 5 V w czasie krótszym niż 1 ns

- filtry typu Π : Łączą kulki ferrytowe z kondensatorami filtrującymi, aby tłumić wysokoczęstotliwościowy szum ESD (>100 MHz)

-

Najlepsze praktyki układania płytek PCB :

- Ciągłe płaszczyzny masy o niskim impedancji (<15 mΩ)

- Minimalna długość ścieżek między urządzeniami TVS a chronionymi układami scalonymi

- Strategiczne oddzielenie sekcji analogowych, cyfrowych i RF w celu zapobiegania sprzężeniu

Gdy te środki są stosowane zgodnie z wytycznymi normy IEC 61000-4-2, mogą one podnieść odporność systemu na wyładowania elektrostatyczne (ESD) o 4–8 kV. Najbardziej odpornościowe projekty integrują ograniczanie napięcia za pomocą elementów TVS z zoptymalizowanym prowadzeniem ścieżek, tworząc przewidywalne, niskoomowe ścieżki odprowadzania energii — kierując ją z dala od wrażliwych węzłów.

Opakowania i procedury obsługi chroniące przed ESD w celu zachowania integralności komponentów

Zachowanie integralności komponentów w całym procesie – od produkcji płytek krzemowych aż po ich końcowe zastosowanie – wymaga ścisłej kontroli sposobu ich pakowania i obsługi. Do tego celu wykorzystuje się kilka kluczowych materiałów. Torby rozpraszające ładunki elektrostatyczne zapobiegają powstawaniu ładunków powierzchniowych dzięki oporności w zakresie od 10⁴ do 10¹¹ omów. Tace przewodzące, wykonane z polimerów wzbogaconych węglem, skutecznie odprowadzają przypadkowe prądy elektryczne. Istnieją również zaawansowane pojemniki metalizowane, które tworzą wielowarstwową ochronę przed zewnętrznymi polami elektrostatycznymi. Podczas transportu elementów specjalne uchwyty do komponentów zapewniają ich stabilne umieszczenie, dzięki czemu nic nie ulega uszkodzeniu w trakcie przewozu. Operacje logistyczne korzystają także z palet odpornych na wyładowania elektrostatyczne (ESD), które zapobiegają uciążliwemu zjawisku triboelektrycznemu, polegającemu na gromadzeniu się ładunków statycznych w wyniku tarcia się materiałów.

Główne zasady, których należy przestrzegać przy obsłudze wrażliwych komponentów, obejmują m.in. zapewnienie uziemienia personelu za pomocą opaski nadgarstkowej, którą sprawdza się codziennie, umieszczenie jonizatorów wokół powierzchni roboczych w celu usuwania pozostałego ładunku elektrostatycznego oraz stosowanie standardowych znaków ostrzegawczych – zwykle żółtych trójkątów na opakowaniach, których znaczenie jest powszechnie znane. Cały ten zestaw działań pozwala utrzymać poziom napięcia elektrostatycznego poniżej 100 V. Badania branżowe wykazują, że utrzymanie tego poziomu zmniejsza tzw. dryf parametrów – czyli pierwszy objaw potencjalnego ukrytego uszkodzenia spowodowanego wyładowaniem elektrostatycznym (ESD). Zgodnie z różnymi raportami z sektorów produkcyjnych, zastosowanie tej metody pozwala zmniejszyć takie przypadki o ponad 30 procent.

Spis treści

- Zrozumienie uszkodzeń spowodowanych przez ESD: typy, przyczyny oraz wpływ na niezawodność komponentów

- Strategie ochrony przed wyładowaniami elektrostatycznymi (ESD): od projektowania ochrony w układzie scalonym po realizację na poziomie systemu

- Opakowania i procedury obsługi chroniące przed ESD w celu zachowania integralności komponentów