Розуміння пошкоджень від ЕСР: типи, причини та вплив на надійність компонентів

Катастрофічні, приховані та параметричні режими відмов

Коли йдеться про електроніку, електростатичний розряд (ESD) може серйозно вплинути на надійність компонентів трьома основними способами. По-перше, це так звані катастрофічні відмови, коли компонент піддається впливу спалахів високої напруги й одразу повністю припиняє працювати. По-друге, існують приховані відмови, які не проявляються відразу, а виявляються значно пізніше. Компоненти можуть успішно пройти всі випробування на перший погляд, але всередині поступово починають деградувати з часом. Це стає серйозною проблемою в майбутньому, коли пристрої несподівано виходять з ладу в критично важливих місцях — наприклад, у лікарнях, літаках або автомобілях. Третій тип — параметричні відмови, що змінюють електричні характеристики роботи компонентів, не призводячи при цьому до їх фізичного пошкодження. Наприклад, зростання струмів витоку або зміна рівнів напруги поступово призводить до погіршення роботи компонентів порівняно з їх номінальними характеристиками. Згідно з останніми даними Асоціації EOS/ESD за 2023 рік, близько третини всіх відмов напівпровідникових виробів під час виробництва спричинені проблемами, пов’язаними з ESD. Коли таке трапляється під час виробництва сучасних інтегральних мікросхем, компанії можуть втратити сотні тисяч доларів США на кожний подібний випадок.

Фізичне деградування: руйнування оксидного шару затвора, пробій діелектрика та пошкодження p-n-переходу

Розглядаючи речі під мікроскопом, електростатичний розряд призводить до структурних пошкоджень трьома основними способами. Щодо MOSFET-транзисторів, відбувається так зване пробиття оксидного шару затвора. Сутність цього явища полягає в тому, що розряд «пробиває» надтонкі шари діелектрика. Ця проблема стає ще більш серйозною по мірі зменшення технологічних норм нижче 10 нанометрів, оскільки товщина таких оксидних шарів іноді становить лише близько 5–10 атомів. Далі йде пробій діелектрика — це, по суті, утворення небажаних провідних шляхів усередині конденсаторів або інших діелектриків, що зазвичай призводить до короткого замикання. Ще однією проблемою є пошкодження p-n-переходів через теплове навантаження: інтенсивне нагрівання сплавляє з’єднання між кремнієвими та металевими компонентами, назавжди змінюючи роботу транзисторів. Більшість таких відмов починаються зі звичайного фізичного контакту людини. Наприклад, просте ходіння по килимі може накопичити близько 1,5 кіловольта заряду. Іншими причинами є некваліфіковане обладнання або забруднення поверхонь, що робить їх надто провідними. Ступінь чутливості пристрою до таких впливів значною мірою залежить від його типу.

- Інтегральні мікросхеми низької напруги : виходять з ладу при <100 В

- Дискретні діоди : зазвичай витримують 2–5 кВ

- Сучасні процесори : можуть пошкоджуватися розрядами нижче 250 В

Стратегії захисту від електростатичного розряду (ESD): від проектування захисту на кристалі до реалізації на рівні системи

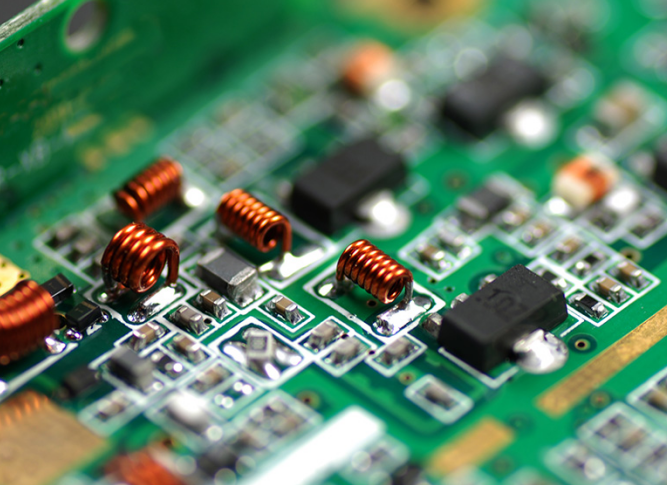

Ефективний захист від ESD вимагає узгодженого багаторівневого підходу — інтеграції засобів захисту безпосередньо в кремній та їх підсилення на рівні друкованої плати й усього пристрою. Ця стратегія «захисту глибокої структури» забезпечує перехоплення короткочасних перешкод до того, як вони досягнуть чутливих електронних компонентів.

Інтегрований захист від ESD на кристалі: діоди, тиристори (SCR) та пристрої з ефектом «snapback»

Структури захисту на кристалі виготовляються безпосередньо в інтегральних мікросхемах для перехоплення подій ESD на рівні виводів. Основні рішення включають:

- Діоди з затиском відводити тимчасові струми до живлячих шин або заземлення, якщо напруга перевищує безпечні порогові значення

- SCR (керовані кремнієві випрямлячі) активувати низькоімпедансні шляхи провідності під час подій з високим струмом за допомогою керованого защелкування

- Пристрої з ефектом «спрачу» (snapback) використовувати конфігурації NMOS/PMOS, які після спрацювання переходять у стан з нижчою напругою та високим струмом

Ці елементи з наносекундною швидкістю реакції обмежують перевищення напруги менш ніж на 10 % від руйнівних рівнів — що є критичним для збереження цілісності оксидних шарів затворів і p-n-переходів. Розробникам необхідно уважно поєднувати міцність захисту з паразитною ємністю, особливо в інтерфейсах високої швидкості (наприклад, PCIe 6.0, USB4), де надлишкова ємність може спотворювати цілісність сигналів при швидкостях понад 5 Гбіт/с.

Системний захист від ЕСР: діоди TVS, фільтрація та розведення друкованої плати для забезпечення надійності

Захист на рівні плати доповнює захисні механізми на кристалі, керуючи тимчасовими імпульсами більшої енергії, які перевищують допустимі межі напівпровідникових компонентів. До основних елементів належать:

- Діоди TVS (подавлення тимчасових перенапруг) розміщено в межах 2 мм від роз’ємів введення/виведення для обмеження напруги до рівня нижче 5 В за час менше ніж 1 нс

- п-подібні фільтри поєднують феритові кульки та декаплюючі конденсатори для пригнічення високочастотного ЕСР-шуму (>100 МГц)

-

Найкращі практики розміщення елементів на друкованій платі :

- Неперервні заземлювальні площини з низьким імпедансом (<15 мОм)

- Мінімальна довжина стежок між пристроями TVS та захищеними ІС

- Стратегічне розділення аналогових, цифрових та РЧ-ділянок для запобігання їх взаємному зв’язку

Якщо ці заходи реалізовано згідно з рекомендаціями стандарту IEC 61000-4-2, вони можуть підвищити стійкість системи до електростатичного розряду на 4–8 кВ. Найбільш надійні конструкції поєднують обмеження напруги за допомогою TVS-елементів із оптимізованим трасуванням, щоб створити передбачувані шляхи розряду з низьким імпедансом — таким чином спрямовуючи енергію подалі від чутливих вузлів.

ЕСР-захисна упаковка та обробка компонентів для збереження їх цілісності

Збереження цілісності компонентів протягом усього процесу — від виготовлення пластина до кінцевого використання — вимагає суворого контролю за їх упаковкою та обробкою. Для цього використовується кілька ключових матеріалів. Статично розсіювальні пакети сприяють зняттю поверхневих зарядів, оскільки їх опір знаходиться в діапазоні від 10⁴ до 10¹¹ Ом. Провідні лотки, виготовлені з полімерів, що містять вуглець, справді відводять сторонні електричні струми. А також існують спеціальні металізовані контейнери, які створюють багаторівневий захист від зовнішніх електростатичних полів. Під час транспортування компонентів спеціальні тримачі забезпечують їх надійне фіксування, щоб нічого не пошкодилося під час перевезення. Операції логістики також виграють від використання ESD-безпечних піддонів, які запобігають неприємному трибоелектричному ефекту, при якому статична електрика накопичується просто внаслідок тертя поверхонь одна об одну.

Основні вимоги, яким необхідно дотримуватися під час роботи з чутливими компонентами, включають забезпечення заземлення персоналу за допомогою браслетів на зап’ястя, які щодня проходять перевірку, розміщення іонізаторів навколо робочих поверхонь для нейтралізації будь-якого залишкового статичного заряду та розміщення стандартних попереджувальних знаків усюди — зазвичай це жовті трикутники на упаковці, значення яких добре відоме всім. У сукупності така організація робочого місця забезпечує рівень статичної електрики нижче 100 вольт. Дослідження в галузі свідчать, що підтримання такого рівня зменшує так званий параметричний дрейф — це, по суті, перший ознака можливої прихованої пошкодженості внаслідок електростатичного розряду (ESD). Згідно з різними звітами виробничих підприємств, такий підхід дозволяє знизити подібні проблеми більш ніж на 30 відсотків.