Memahami Kerosakan ESD: Jenis, Punca, dan Impak terhadap Kebolehpercayaan Komponen

Mod Kegagalan Membawa Maut, Tersembunyi, dan Berparameter

Apabila membabitkan elektronik, pelepasan elektrostatik atau ESD benar-benar boleh menjejaskan kebolehpercayaan komponen dalam tiga cara utama. Pertama, terdapat apa yang kita namakan kegagalan katas (catastrophic failures), iaitu apabila sesuatu komponen dipukul oleh lonjakan voltan tinggi dan terus berhenti berfungsi sepenuhnya serta-merta. Kedua, terdapat kegagalan laten yang terselindung—kegagalan ini tidak kelihatan sehingga jangka masa yang jauh kemudian. Komponen mungkin lulus semua ujian pada pandangan pertama, tetapi di dalamnya proses pemerosotan berlaku secara perlahan dari masa ke masa. Ini menjadi masalah besar di kemudian hari apabila peranti gagal secara tidak dijangka di tempat-tempat penting seperti hospital, kapal terbang, atau kereta. Jenis ketiga ialah kegagalan parameter, iaitu perubahan dalam cara sesuatu beroperasi secara elektrik tanpa sebenarnya mengalami kerosakan fizikal. Contohnya ialah arus bocor yang lebih tinggi atau aras voltan yang berbeza, yang secara beransur-ansur menyebabkan komponen berprestasi lebih rendah daripada tahap yang sepatutnya. Menurut angka terkini daripada Persatuan EOS/ESD pada tahun 2023, kira-kira satu pertiga daripada semua kegagalan semikonduktor semasa fasa pembuatan disebabkan oleh masalah ESD. Dan apabila ini berlaku dalam pengeluaran litar bersepadu lanjutan, syarikat-syarikat boleh mengalami kerugian berjumlah ratusan ribu dolar AS bagi setiap insiden.

Degradasi Fizikal: Kerosakan Oksida Gerbang, Kebocoran Dielektrik, dan Kerosakan Sambungan

Dengan memeriksa benda-benda di bawah mikroskop, pelepasan elektrostatik menyebabkan masalah struktural dalam tiga cara utama. Dalam kes MOSFET, fenomena yang berlaku dikenali sebagai kegagalan oksida gerbang. Secara asasnya, pelepasan tersebut menembusi lapisan penebat yang sangat nipis ini. Masalah ini menjadi semakin serius apabila teknologi semakin mengecil hingga kurang daripada 10 nanometer, kerana lapisan oksida ini kadangkala hanya setebal kira-kira 5 hingga 10 atom. Seterusnya terdapat kegagalan dielektrik, iaitu pembentukan laluan konduktif yang tidak diingini di dalam kapasitor atau penebat lain, yang biasanya mengakibatkan litar pintas. Isu lain ialah kerosakan sambungan akibat tekanan haba. Habah yang sangat tinggi meleburkan sambungan antara bahagian silikon dan logam, sehingga mengubah cara kerja transistor secara kekal. Kebanyakan kegagalan ini bermula dengan sentuhan manusia biasa. Hanya berjalan di atas permaidani sahaja boleh menghasilkan cas sebanyak kira-kira 1.5 kilovolt. Punca lain termasuk alat yang tidak sesuai atau habuk yang menyebabkan permukaan menjadi terlalu konduktif. Tahap kerentanan suatu komponen bergantung banyak kepada jenis peranti yang dimaksudkan.

- IC voltan rendah : Gagal pada <100 V

- Dioda diskret : Biasanya tahan terhadap 2–5 kV

- Pemproses lanjutan : Boleh rosak akibat pelepasan di bawah 250 V

Strategi Perlindungan ESD: Daripada Reka Bentuk Dalam Cip hingga Pelaksanaan di Tahap Sistem

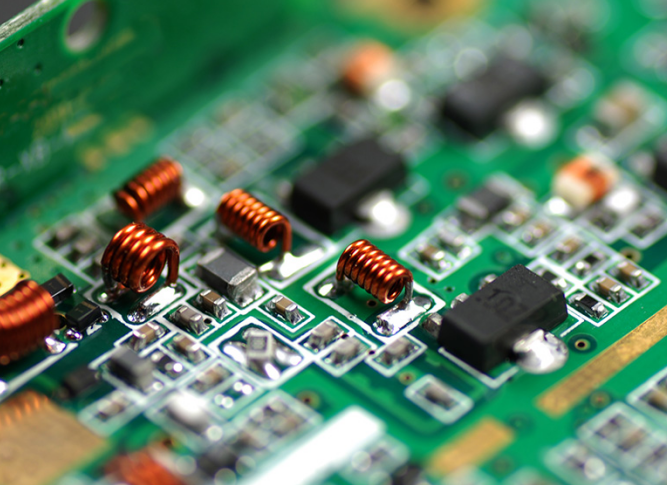

Perlindungan ESD yang berkesan memerlukan pendekatan berkoordinasi dan berbilang lapisan—mengintegrasikan langkah-langkah keselamatan secara langsung ke dalam silikon sambil mengukuhkannya pada tahap papan litar dan sistem. Strategi pertahanan-melalui-kedalaman ini memastikan ancaman sementara dihalang sebelum mencapai litar yang sensitif.

Perlindungan ESD Terkamir dalam Cip: Dioda, SCR, dan Peranti Snapback

Struktur perlindungan dalam cip dibuat secara langsung ke dalam litar bersepadu untuk menghalang peristiwa ESD pada tahap pin. Penyelesaian utama termasuk:

- Diod Pengapit : Mengalihkan arus sementara ke rel kuasa atau tanah apabila voltan melebihi ambang keselamatan

- SCR (Penyearah Terkawal Silikon) : Mengaktifkan laluan pengaliran impedans-rendah semasa peristiwa arus tinggi melalui kawalan 'latch-up'

- Peranti 'Snapback' : Memanfaatkan konfigurasi NMOS/PMOS yang berpindah ke keadaan voltan-rendah dan arus-tinggi selepas pencetus diaktifkan

Unsur-unsur ini yang bertindak balas dalam nanosaat menghadkan lonjakan voltan kepada kurang daripada 10% daripada tahap yang boleh merosakkan—sangat penting untuk mengekalkan keteguhan oksida gerbang dan integriti simpang. Pereka mesti secara teliti mengimbangkan kekuatan perlindungan dengan kapasitans parasitik, terutamanya pada antara muka kelajuan-tinggi (contohnya, PCIe 6.0, USB4), di mana kapasitans berlebihan boleh mengganggu integriti isyarat pada kelajuan melebihi 5 Gbps.

Perlindungan ESD Tahap Sistem: Diod TVS, Penapisan, dan Susun Atur PCB untuk Ketahanan

Perlindungan tahap papan melengkapi pertahanan dalam-cip dengan menguruskan transien tenaga-tinggi yang melebihi had toleransi semikonduktor. Unsur penting termasuk:

- Diod TVS (Penekanan Voltan Transien) : Diletakkan dalam jarak 2 mm daripada penyambung I/O untuk mengawal voltan di bawah 5 V dalam masa kurang daripada 1 ns

- penapis Π : Menggabungkan manik ferit dan kapasitor pendekup untuk mengurangkan gangguan ESD berfrekuensi tinggi (>100 MHz)

-

Amalan terbaik susun atur PCB :

- Satah tanah yang berterusan dengan rintangan rendah (<15 mΩ)

- Panjang jejak yang minimum antara peranti TVS dan IC yang dilindungi

- Pemisahan strategik bahagian analog, digital, dan RF untuk mengelakkan pengaruh bersilang

Apabila dilaksanakan mengikut garis panduan IEC 61000-4-2, langkah-langkah ini boleh meningkatkan ketahanan ESD peringkat sistem sebanyak 4–8 kV. Reka bentuk paling kukuh menggabungkan pengawalan TVS dengan penghalaan yang dioptimumkan untuk membentuk laluan pelepasan tenaga yang boleh diramalkan dan berintangan rendah—mengalihkan tenaga jauh daripada nod yang sensitif.

Pembungkusan dan Pengendalian Pelindung ESD untuk Integriti Komponen

Menjaga komponen tetap utuh sepanjang keseluruhan proses—mulai dari pembuatan wafer hingga penggunaan akhir—memerlukan kawalan ketat terhadap cara pembungkusan dan penanganannya. Terdapat beberapa bahan utama yang digunakan untuk tujuan ini. Beg statik dissipatif membantu menghilangkan cas permukaan kerana mempunyai tahap rintangan antara 10^4 hingga 10^11 ohm. Dulang konduktif yang diperbuat daripada polimer berbeban karbon benar-benar mengalirkan arus elektrik liar. Selain itu, terdapat bekas bermetalisis canggih yang mencipta pelbagai lapisan perlindungan terhadap medan elektrostatik luaran. Ketika memindahkan komponen, pemegang komponen khas memastikan semua barang kekal pada kedudukannya supaya tiada apa-apa yang rosak semasa penghantaran. Operasi logistik juga mendapat manfaat daripada palet ESD selamat yang menghalang kesan triboelektrik yang mengganggu—iaitu fenomena di mana cas statik terbina hanya akibat geseran antara dua objek.

Perkara utama yang perlu diikuti orang apabila mengendalikan komponen sensitif termasuk memastikan pekerja dipasang ke bumi menggunakan tali pergelangan tangan yang diuji setiap hari, menempatkan pengion di sekitar permukaan kerja untuk menghilangkan sebarang cas elektrostatik yang tertinggal, serta memasang tanda amaran piawai di mana-mana sahaja—biasanya segitiga kuning pada bungkusan yang semua orang tahu maksudnya. Secara keseluruhan, susunan ini mengekalkan aras elektrik statik di bawah 100 volt. Kajian industri menunjukkan bahawa mengekalkan aras ini dapat mengurangkan suatu fenomena yang dikenali sebagai 'parametric drift', iaitu tanda awal bahawa mungkin berlaku kerosakan ESD tersembunyi. Kajian menunjukkan pendekatan ini boleh mengurangkan isu-isu sedemikian sebanyak lebih daripada 30 peratus, berdasarkan pelbagai laporan dari sektor pembuatan.