Compreendendo os Danos por Descarga Eletrostática (ESD): Tipos, Causas e Impacto na Confiabilidade dos Componentes

Modos de Falha Catastrófica, Latente e Paramétrica

Quando se trata de eletrônicos, a descarga eletrostática (ESD) pode realmente comprometer a confiabilidade dos componentes de três maneiras principais. Primeiro, há o que chamamos de falhas catastróficas, nas quais um componente é atingido por picos de alta tensão e simplesmente deixa de funcionar por completo imediatamente. Em seguida, há as falhas latentes, mais sutis, que não se manifestam até muito tempo depois: os componentes podem passar em todos os testes à primeira vista, mas, internamente, começam a se degradar lentamente ao longo do tempo. Isso torna-se um grande problema no futuro, quando dispositivos falham inesperadamente em locais críticos, como hospitais, aviões ou automóveis. O terceiro tipo é o das falhas paramétricas, que alteram o comportamento elétrico dos componentes sem, contudo, danificá-los fisicamente. Exemplos incluem correntes de fuga mais elevadas ou níveis de tensão diferentes, que gradualmente fazem com que os componentes apresentem desempenho inferior ao esperado. De acordo com dados recentes da EOS/ESD Association, de 2023, cerca de um terço de todas as falhas em semicondutores durante a fabricação são causadas por problemas relacionados à ESD. E, quando isso ocorre na produção de circuitos integrados avançados, as empresas podem acabar perdendo centenas de milhares de dólares por incidente.

Degradação Física: Ruptura do Óxido da Porta, Ruptura Dielétrica e Danos na Junção

Ao observar as coisas sob um microscópio, a descarga eletrostática causa problemas estruturais de três maneiras principais. No caso dos MOSFETs, o que ocorre é chamado de ruptura do óxido da porta. Basicamente, a descarga perfura essas camadas isolantes extremamente finas. Esse problema torna-se ainda maior à medida que a tecnologia avança para dimensões inferiores a 10 nanômetros, pois essas camadas de óxido têm, por vezes, apenas cerca de 5 a 10 átomos de espessura. Em seguida, há a ruptura dielétrica, que basicamente significa a criação de caminhos condutores indesejados no interior de capacitores ou outros isolantes, geralmente resultando em curtos-circuitos. Outro problema é a danificação das junções causada pela tensão térmica: o calor intenso funde as conexões entre as partes de silício e metal, alterando permanentemente o funcionamento dos transistores. A maioria dessas falhas começa com o simples contato humano habitual. Apenas caminhar sobre um carpete pode gerar uma carga de aproximadamente 1,5 quilovolts. Outras causas incluem ferramentas inadequadas ou sujeira que torna as superfícies excessivamente condutoras. O grau de vulnerabilidade de um componente depende muito do tipo de dispositivo em questão.

- CIs de baixa tensão : Falham em <100 V

- Diodos discretos : Normalmente suportam 2–5 kV

- Processadores avançados : Podem ser danificados por descargas inferiores a 250 V

Estratégias de proteção contra ESD: Da concepção no chip à implementação no nível do sistema

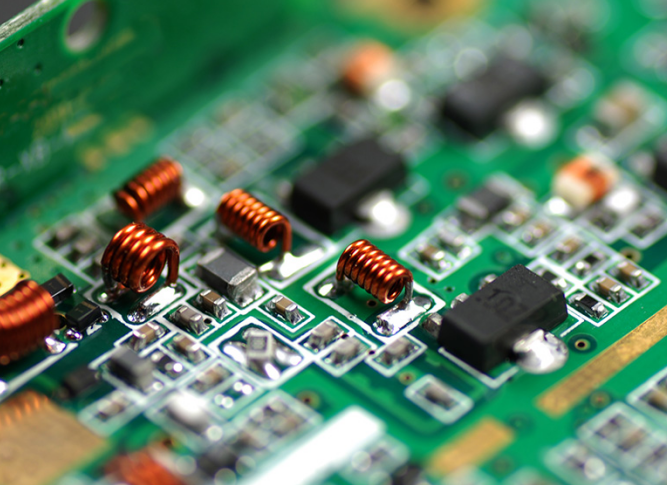

Uma proteção eficaz contra ESD exige uma abordagem coordenada e multicamadas — integrando proteções diretamente no silício, ao mesmo tempo que as reforça nos níveis da placa e do sistema. Essa estratégia de defesa em profundidade garante que ameaças transitórias sejam interceptadas antes de atingirem circuitos sensíveis.

Proteção contra ESD integrada no chip: Diodos, SCRs e dispositivos de snapback

As estruturas de proteção no chip são fabricadas diretamente nos circuitos integrados para interceptar eventos de ESD no nível dos pinos. As principais soluções incluem:

- Diodos de Clamp : Desvia correntes transitórias para as trilhas de alimentação ou para o terra assim que a tensão ultrapassa os limiares seguros

- SCRs (Retificadores Controlados de Silício) : Ativa caminhos de condução de baixa impedância durante eventos de alta corrente por meio de um bloqueio controlado

- Dispositivos snapback : Explora configurações NMOS/PMOS que transicionam para estados de baixa tensão e alta corrente após a ativação

Esses elementos de resposta em nanosegundos limitam a sobretensão a menos de 10% dos níveis destrutivos — fundamental para preservar as oxidações das portas e a integridade das junções. Os projetistas devem equilibrar cuidadosamente a eficácia da proteção com a capacitância parasita, especialmente em interfaces de alta velocidade (por exemplo, PCIe 6.0, USB4), nas quais uma capacitância excessiva pode distorcer a integridade do sinal acima de 5 Gbps.

Proteção contra ESD no nível de sistema: Diodos TVS, filtragem e disposição de PCB para robustez

A proteção no nível da placa complementa as defesas integradas ao chip, gerenciando transientes de maior energia que excedem as tolerâncias dos semicondutores. Os elementos essenciais incluem:

- Diodos TVS (Supressão de Tensão Transitória) : Colocado a menos de 2 mm dos conectores de entrada/saída (I/O) para limitar as tensões abaixo de 5 V em menos de 1 ns

- filtros Π : Combinam pérolas de ferrite e capacitores de desacoplamento para atenuar ruídos de ESD de alta frequência (> 100 MHz)

-

Práticas recomendadas para o projeto de PCB :

- Planos de terra contínuos e de baixa impedância (< 15 mΩ)

- Comprimento mínimo de trilha entre os dispositivos TVS e os CIs protegidos

- Separação estratégica das seções analógica, digital e RF para evitar acoplamento

Quando implementadas conforme as diretrizes da norma IEC 61000-4-2, essas medidas podem elevar a imunidade do sistema a descargas eletrostáticas (ESD) em 4–8 kV. Os projetos mais robustos integram a limitação por dispositivos TVS com roteamento otimizado, estabelecendo caminhos previsíveis e de baixa impedância para a descarga — desviando a energia para longe de nós sensíveis.

Embalagem e manuseio protetores contra ESD para preservação da integridade dos componentes

Manter os componentes intactos durante todo o processo, desde a fabricação do wafers até a utilização final, exige um controle rigoroso de como são embalados e manuseados. Existem diversos materiais-chave utilizados para essa finalidade. Sacos dissipadores de estática ajudam a eliminar cargas superficiais, pois possuem níveis de resistência entre 10^4 e 10^11 ohms. Bandejas condutivas fabricadas com polímeros carregados com carbono conduzem efetivamente quaisquer correntes elétricas indesejadas. E há ainda aqueles sofisticados recipientes metalizados que criam múltiplas camadas de proteção contra campos eletrostáticos externos. Ao transportar componentes, suportes especiais mantêm tudo em posição, evitando danos durante o trânsito. As operações logísticas também se beneficiam de paletes seguras para ESD, que impedem aquele incômodo efeito triboelétrico, no qual a eletricidade estática se acumula simplesmente pelo atrito entre superfícies.

As principais medidas que as pessoas devem adotar ao manipular componentes sensíveis incluem garantir que os funcionários estejam aterrados por meio da utilização de pulseiras antiestáticas, testadas diariamente; posicionar ionizadores ao redor das superfícies de trabalho para eliminar qualquer carga eletrostática residual; e afixar placas-padrão de advertência em todos os locais — normalmente triângulos amarelos nas embalagens, cujo significado é amplamente reconhecido. Conjuntamente, essa configuração mantém os níveis de eletricidade estática abaixo de 100 volts. Pesquisas setoriais indicam que manter esse nível reduz um fenômeno denominado deriva paramétrica, que constitui basicamente o primeiro sinal de que pode estar ocorrendo dano oculto por descarga eletrostática (ESD). Estudos apontam que essa abordagem pode reduzir tais problemas em mais de 30%, conforme diversos relatórios provenientes de setores industriais.