Porozumění poškození způsobenému elektrostatickým výbojem (ESD): typy, příčiny a dopad na spolehlivost komponent

Katastrofální, latentní a parametrické režimy poruch

Pokud jde o elektroniku, elektrostatický výboj (ESD) může výrazně narušit spolehlivost součástek třemi hlavními způsoby. Za prvé jsou to tzv. katastrofické poruchy, při nichž součástka zasáhne vysokonapěťový špičkový impuls a okamžitě zcela přestane fungovat. Za druhé existují tyto nenápadné skryté poruchy, které se projeví až mnohem později. Součástky mohou na první pohled projít všemi testy, avšak uvnitř se postupně začnou degradovat. Toto se stává vážným problémem v pozdější fázi, kdy zařízení neočekávaně selže v důležitých prostředích, jako jsou nemocnice, letadla nebo automobily. Třetím typem jsou parametrické poruchy, které změní elektrické chování součástek, aniž by je fyzicky poškodily. Jedná se například o vyšší unikající proudy nebo odlišné úrovně napětí, které postupně zhoršují výkon součástek pod jejich specifikovanou úroveň. Podle nedávných údajů z roku 2023 od organizace EOS/ESD Association je přibližně jedna třetina všech poruch polovodičů během výroby způsobena problémy s ESD. A pokud se taková událost odehraje při výrobě pokročilých integrovaných obvodů, mohou firmy v důsledku jediného incidentu ztratit stovky tisíc dolarů.

Fyzické degradace: průraz hradlového oxidu, průraz dielektrika a poškození přechodu

Pohled na věci pod mikroskopem ukazuje, že elektrostatický výboj způsobuje strukturální problémy třemi hlavními způsoby. U tranzistorů řízených polem (MOSFET) dochází k jevu označovanému jako průraz hradlového oxidu. V podstatě výboj prostupuje těmito extrémně tenkými izolačními vrstvami. Tento problém se zhoršuje s postupujícím zmenšováním technologie pod 10 nanometrů, neboť tloušťka těchto oxidových vrstev někdy činí pouhých 5 až 10 atomů. Dále existuje průraz dielektrika, což v podstatě znamená vznik nežádoucích vodivých cest uvnitř kondenzátorů či jiných izolantů, často vedoucí ke zkratům. Dalším problémem je poškození přechodu způsobené tepelným napětím. Intenzivní teplo roztaví spoje mezi křemíkem a kovovými částmi, čímž trvale změní způsob fungování tranzistorů. Většina těchto poruch má začátek v běžném fyzickém kontaktu s člověkem. Stačí prosté chůze po koberci, aby se nahromadilo asi 1,5 kV náboje. Mezi další příčiny patří nevhodné nástroje nebo nečistoty, které způsobují příliš snadnou vodivost povrchů. Míra citlivosti dané součástky závisí výrazně na tom, o jaký typ zařízení se jedná.

- Integrované obvody nízkého napětí : Selžou při napětí < 100 V

- Diskrétní diody : Obvykle vydrží 2–5 kV

- Pokročilé procesory : Mohou být poškozeny výboji nižšími než 250 V

Strategie ochrany proti elektrostatickému výboji (ESD): od návrhu ochrany na čipu až po implementaci na úrovni celého systému

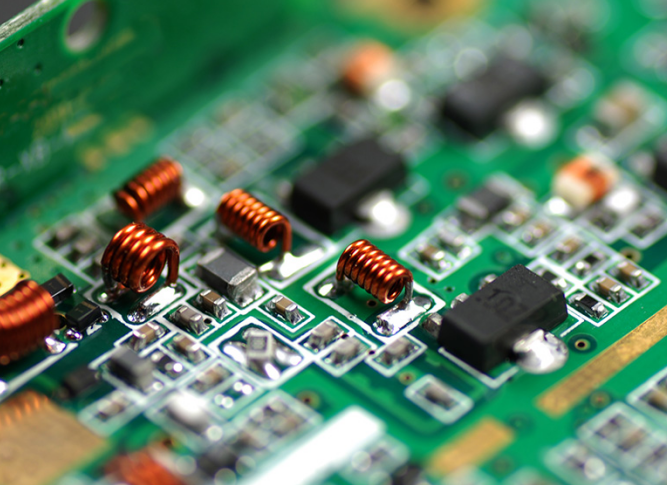

Účinná ochrana proti ESD vyžaduje koordinovaný, vícevrstvý přístup – integruje bezpečnostní opatření přímo do křemíku a zároveň je posiluje na úrovni desky plošných spojů a celého systému. Tato strategie obrany na několika úrovních zajistí, že přechodné hrozby budou zachyceny dříve, než dosáhnou citlivých obvodů.

Integrovaná ochrana proti ESD na čipu: diody, tyristory (SCR) a zařízení se jevem snapback

Ochranné struktury na čipu jsou vyráběny přímo v integrovaných obvodech, aby zachytily události ESD na úrovni vývodů. Mezi klíčová řešení patří:

- Zkratové diody odvede přechodné proudy do napájecích sběrnic nebo uzemnění, jakmile napětí překročí bezpečné meze

- SCR (řízené křemíkové usměrňovače) aktivuje vedení s nízkou impedancí během událostí s vysokým proudem prostřednictvím řízeného zapnutí (latch-up)

- Zařízení se zpětným průrazem (snapback) využívá konfigurace NMOS/PMOS, které po spuštění přecházejí do stavů s nižším napětím a vyšším proudem

Tyto prvky s odezvou v řádu nanosekund omezují překmit napětí na méně než 10 % ničivé úrovně – což je rozhodující pro uchování integrity oxidační vrstvy u hradel a přechodů. Návrháři musí pečlivě vyvážit sílu ochrany vůči parazitní kapacitě, zejména u rozhraní s vysokou rychlostí přenosu (např. PCIe 6.0, USB4), kde nadměrná kapacita může narušit integritu signálu při rychlostech vyšších než 5 Gbps.

Systémová ESD ochrana: TVS diody, filtrace a uspořádání plošného spoje pro zvýšenou odolnost

Ochrana na úrovni desky doplňuje ochranu integrovanou přímo do čipu tím, že zpracovává přechodné jevy vyšší energie, které přesahují povolené limity polovodičových součástek. Mezi základní prvky patří:

- TVS (ochranné) diody umístěno do vzdálenosti 2 mm od I/O konektorů, aby napětí omezilo na hodnotu pod 5 V během méně než 1 ns

- π-filtry kombinují feritové členy a odrušovací kondenzátory k potlačení vysokofrekvenčního ESD šumu (> 100 MHz)

-

Doporučené postupy pro návrh plošných spojů (PCB) :

- Souvislé uzemňovací roviny s nízkou impedancí (< 15 mΩ)

- Minimální délka vodivých tras mezi zařízeními TVS a chráněnými integrovanými obvody

- Strategické oddělení analogových, digitálních a RF částí za účelem prevence vazby

Při dodržení pokynů normy IEC 61000-4-2 mohou tyto opatření zvýšit úroveň odolnosti systému vůči ESD o 4–8 kV. Nejodolnější návrhy kombinují omezení napětí pomocí prvků TVS s optimalizovaným směrováním tras, čímž vytvářejí předvídatelné, nízkoimpedanční cesty pro vybíjení – tedy odvádějí energii pryč od citlivých uzlů.

ESD ochranné balení a manipulace pro zachování integrity komponent

Udržení součástí nepoškozených po celou dobu procesu – od výroby polovodičových destiček až po konečné použití – vyžaduje přísnou kontrolu způsobu jejich balení a manipulace. K tomuto účelu se používá několik klíčových materiálů. Staticky disipativní taštičky pomáhají odstranit povrchové náboje, protože mají odpor v rozmezí 10⁴ až 10¹¹ ohmů. Vodivé dříkované zásobníky vyrobené z polymerů naplněných uhlíkem skutečně odvádějí jakékoliv náhodné elektrické proudy. A poté jsou tu ty pokročilé metalizované nádoby, které vytvářejí vícevrstvou ochranu proti vnějším elektrostatickým polím. Při přepravě součástí zajišťují speciální držáky součástí jejich pevné uložení, aby nedošlo k poškození během přepravy. Logistické operace také profitují z ESD-bezpečných palet, které brání tomu otravnému triboelektrickému jevu, při němž se statická elektřina hromadí pouhým třením předmětů o sebe.

Klíčové postupy, kterých se lidé musí držet při manipulaci se citlivými komponenty, zahrnují například zajištění uzemnění zaměstnanců pomocí náramkových uzemňovacích pásek, jež se testují každý den, umístění ionizátorů kolem pracovních ploch za účelem eliminace jakéhokoli zbytkového elektrostatického náboje a umístění standardních varovných značek všude – obvykle žlutých trojúhelníků na baleních, jejichž význam je všem znám. Tato komplexní opatření společně udržují úroveň elektrostatického napětí pod 100 V. Průmyslový výzkum ukazuje, že udržování této úrovně snižuje tzv. parametrický drift, což je v podstatě první známka možné skryté poškození způsobené elektrostatickým výbojem (ESD). Různé zprávy z výrobních odvětví uvádějí, že tento přístup může takové problémy snížit o více než 30 procent.

Obsah

- Porozumění poškození způsobenému elektrostatickým výbojem (ESD): typy, příčiny a dopad na spolehlivost komponent

- Strategie ochrany proti elektrostatickému výboji (ESD): od návrhu ochrany na čipu až po implementaci na úrovni celého systému

- ESD ochranné balení a manipulace pro zachování integrity komponent