Verständnis von ESD-Schäden: Arten, Ursachen und Auswirkungen auf die Zuverlässigkeit von Komponenten

Katastrophale, latente und parametrische Ausfallmodi

Wenn es um Elektronik geht, kann elektrostatische Entladung (ESD) die Zuverlässigkeit von Komponenten auf drei wesentliche Arten beeinträchtigen. Erstens gibt es sogenannte katastrophale Ausfälle, bei denen eine Komponente durch Hochspannungsimpulse getroffen wird und sofort vollständig ausfällt. Zweitens existieren diese heimtückischen latenten Ausfälle, die sich erst viel später bemerkbar machen: Komponenten bestehen zwar zunächst alle Tests auf den ersten Blick, doch im Inneren beginnen sie langsam über die Zeit hinweg zu degradieren. Dies wird später zu einem gravierenden Problem, wenn Geräte unerwartet an kritischen Einsatzorten wie Krankenhäusern, Flugzeugen oder Automobilen versagen. Die dritte Art sind parametrische Ausfälle, bei denen sich das elektrische Verhalten verändert, ohne dass die Komponente tatsächlich defekt wird. Dazu zählen beispielsweise erhöhte Leckströme oder abweichende Spannungsniveaus, die dazu führen, dass Komponenten schrittweise schlechter funktionieren, als sie sollten. Laut aktuellen Zahlen der EOS/ESD Association aus dem Jahr 2023 gehen etwa ein Drittel aller Halbleiterausfälle während der Fertigung auf ESD-Probleme zurück. Und wenn dies bei der Herstellung hochentwickelter integrierter Schaltungen geschieht, können Unternehmen pro Vorfall Hunderttausende Dollar verlieren.

Physikalischer Abbau: Durchschlag der Gate-Oxidschicht, Dielektrikum-Durchschlag und Übergangsbeschädigung

Wenn man Dinge unter dem Mikroskop betrachtet, verursacht elektrostatische Entladung strukturelle Probleme auf drei Hauptwegen. Bei MOSFETs spricht man von einer Durchschlagsschädigung der Gate-Oxidschicht. Grundlegend gesagt, durchschlägt die Entladung diese extrem dünnen Isolationsschichten. Dies wird zu einem größeren Problem, wenn die Technologie kleiner als 10 Nanometer wird, da diese Oxidschichten manchmal nur etwa 5 bis 10 Atome dick sind. Dann gibt es die Dielektrikum-Durchschlagsschädigung, bei der unerwünschte leitfähige Pfade innerhalb von Kondensatoren oder anderen Isolatoren entstehen – meist führt dies zu Kurzschlüssen. Ein weiteres Problem ist die Übergangsschädigung durch thermische Belastung: Die intensive Hitze schmilzt die Verbindungen zwischen Silizium- und Metallteilen und verändert die Funktionsweise der Transistoren dauerhaft. Die meisten dieser Ausfälle beginnen mit ganz gewöhnlichem menschlichen Kontakt. Allein das Gehen über einen Teppich kann eine Ladung von etwa 1,5 Kilovolt erzeugen. Weitere Ursachen sind ungeeignete Werkzeuge oder Schmutz, der Oberflächen zu leicht leitfähig macht. Wie anfällig ein Gerät ist, hängt stark davon ab, um welchen Geräte-Typ es sich handelt.

- Niederspannungs-ICs : Versagen bei < 100 V

- Diskrete Dioden : Halten typischerweise 2–5 kV stand

- Hochentwickelte Prozessoren : Können bereits durch Entladungen unterhalb von 250 V beschädigt werden

ESD-Schutzstrategien: Von der On-Chip-Entwicklung bis zur Systemebene

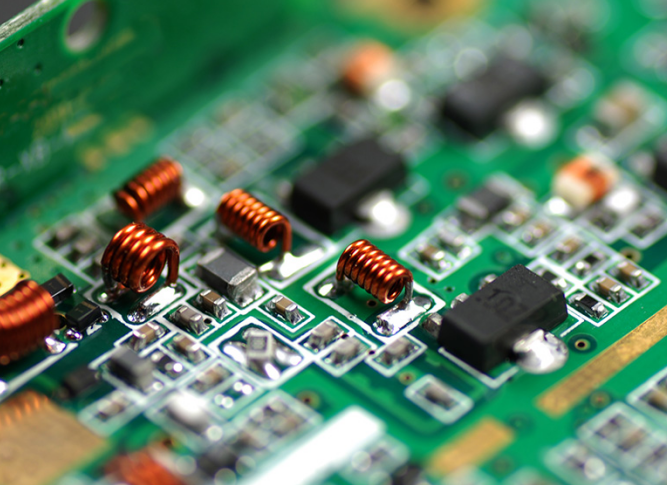

Ein wirksamer ESD-Schutz erfordert einen koordinierten, mehrschichtigen Ansatz – wobei Schutzmaßnahmen direkt in den Siliziumchip integriert und gleichzeitig auf Leiterplatten- und Systemebene verstärkt werden. Diese mehrstufige Verteidigungsstrategie stellt sicher, dass transiente Störgrößen abgefangen werden, bevor sie empfindliche Schaltkreise erreichen.

Integrierter On-Chip-ESD-Schutz: Dioden, SCRs und Snapback-Bauelemente

On-Chip-Schutzstrukturen werden direkt in integrierte Schaltungen gefertigt, um ESD-Ereignisse auf Pin-Ebene abzufangen. Wichtige Lösungen umfassen:

- Freilaufdioden leitet transiente Ströme an die Versorgungsschienen oder Masse ab, sobald die Spannung sichere Schwellenwerte überschreitet

- SCRs (Silicon Controlled Rectifiers) aktiviert niederohmige Leitpfade während hochstromstarker Ereignisse durch gesteuertes Latch-up

- Snapback-Bauelemente nutzen NMOS-/PMOS-Konfigurationen, die nach der Auslösung in einen Zustand mit niedrigerer Spannung und höherem Strom übergehen

Diese nanosekundenschnellen Elemente begrenzen die Spannungsüberschwingung auf weniger als 10 % zerstörerischer Werte – entscheidend für den Erhalt von Gateoxiden und Übergangsintegrität. Konstrukteure müssen Schutzstärke und parasitäre Kapazität sorgfältig abwägen, insbesondere bei Hochgeschwindigkeitsschnittstellen (z. B. PCIe 6.0, USB4), bei denen eine zu hohe Kapazität die Signalintegrität oberhalb von 5 Gbps beeinträchtigen kann.

ESD-Schutz auf Systemebene: TVS-Dioden, Filterung und Leiterplattenlayout für Robustheit

Platinenbasierter Schutz ergänzt die chipinternen Schutzmaßnahmen, indem er Transienten mit höherer Energie bewältigt, die über die Toleranzgrenzen der Halbleiter hinausgehen. Zu den wesentlichen Komponenten zählen:

- TVS-Dioden (Transient Voltage Suppression-Dioden) : Wird innerhalb von 2 mm von I/O-Anschlüssen platziert, um Spannungen unter 5 V in weniger als 1 ns zu begrenzen

- π-Filter : Kombinieren Ferritperlen und Entkopplungskondensatoren, um hochfrequentes ESD-Rauschen (> 100 MHz) zu dämpfen

-

Empfohlene Praktiken für das Leiterplatten-Layout :

- Kontinuierliche, niederohmige Masseebenen (< 15 mΩ)

- Minimale Leiterbahnlänge zwischen TVS-Bauelementen und geschützten ICs

- Strategische Trennung der analogen, digitalen und HF-Bereiche, um Kopplungseffekte zu vermeiden

Wenn diese Maßnahmen gemäß den Richtlinien der IEC 61000-4-2 umgesetzt werden, kann die System-ESD-Immunität um 4–8 kV erhöht werden. Die robustesten Designs kombinieren TVS-Spannungsbegrenzung mit optimiertem Routing, um vorhersehbare, niederohmige Ableitpfade zu schaffen – wodurch die Energie von empfindlichen Knotenpunkten abgeleitet wird.

ESD-Schutzverpackung und -handhabung zur Gewährleistung der Komponentenintegrität

Die Aufrechterhaltung der Integrität von Komponenten während des gesamten Prozesses – von der Waferfertigung bis hin zum endgültigen Einsatz – erfordert eine strenge Kontrolle über Verpackung und Handhabung. Hierfür kommen mehrere Schlüsselmaterialien zum Einsatz. Statistisch ableitende Beutel helfen dabei, Oberflächenladungen abzuleiten, da sie einen Widerstand im Bereich von 10^4 bis 10^11 Ohm aufweisen. Leitfähige Behälter aus kohlenstoffgefüllten Polymeren leiten tatsächlich unerwünschte elektrische Ströme ab. Und dann gibt es noch jene hochentwickelten metallisierten Behälter, die mehrschichtigen Schutz gegen externe elektrostatische Felder bieten. Bei der Transportierung von Bauteilen sorgen spezielle Komponentenhalter dafür, dass alle Teile sicher fixiert bleiben und während des Transports nicht beschädigt werden. Auch Logistikprozesse profitieren von ESD-sicheren Paletten, die den lästigen triboelektrischen Effekt verhindern, bei dem durch Reibung statische Elektrizität entsteht.

Die wichtigsten Punkte, die bei der Handhabung empfindlicher Komponenten beachtet werden müssen, sind beispielsweise die Sicherstellung, dass das Personal mithilfe von Handgelenkbandagen geerdet ist, die täglich getestet werden, die Platzierung von Ionisatoren rund um die Arbeitsflächen, um verbleibende elektrostatische Ladungen abzuleiten, sowie die Anbringung der üblichen Warnhinweise an allen relevanten Stellen – in der Regel gelbe Dreiecke auf Verpackungen, deren Bedeutung allgemein bekannt ist. Insgesamt hält diese Maßnahmenkombination die elektrostatischen Spannungsniveaus unter 100 Volt. Branchenforschung zeigt, dass die Einhaltung dieses Niveaus ein Phänomen namens „parametrischer Drift“ reduziert, das im Grunde das erste Anzeichen für mögliche verborgene ESD-Schäden darstellt. Untersuchungen zufolge kann dieser Ansatz solche Probleme laut verschiedenen Berichten aus der Fertigungsindustrie um mehr als 30 Prozent senken.