Deall Niwed ESD: Mathau, Achosion a'r Effaith ar Hygrededd Cydran

Moddau Methu Catastrophig, Anweithredig a Pharamedrig

Pan fydd yn mynd i electronig, gall gollwng electrostatic neu ESD wirioneddol amharu ar hygrediad cydran mewn tri ffordd brif. Yn gyntaf, mae'r rhai rydym yn eu galw'n methiadau catastroffig, lle mae rhywbeth yn cael ei daro gan y sbigiau uchel o gynhwysiant a sefydlu'n llwyr ar unwaith. Yna mae'r methiadau cudd hynny sydd ddim yn dangos tan hwnt yn hwyrach. Gall cydrannau basio pob prawf ar olwg cyntaf, ond o fewn iddynt maen nhw'n dechrau dirywio yn araf dros amser. Mae hyn yn dod yn broblem fawr yn y dyfodol pan mae dyfeisiau'n methu'n annisgwyl mewn lleoedd pwysig fel ysbytai, awyrennau, neu geir. Y math trydydd yw'r methiadau parametrig sydd yn newid sut mae pethau'n gweithio'n electronig heb eu torri'n wirioneddol. Meddwl am bethau fel cy currents llygredd uwch na'r arfer neu lefelau gwahanol o gynhwysiant sydd yn gwneud i gydrannau weithio'n waelach na'u bod yn disgwyl yn araf. Yn ôl y rhifau diweddar gan Gyngres EOS/ESD yn 2023, tua thri chwarter o'r methiadau ar semiconductors yn ystod y cynhyrchu yn cael eu harwain gan broblemau ESD. A phan fydd hyn yn digwydd yn y cynhyrchu cylchedau integredig uwch, gall cwmnïau ddod i golli cannoedd o filiwnau o doleri America bob achos.

Dirwad Corfforol: Torriadau o Ocsid y Gerdd, Toriadau Dielectrig, a Damwain Cyngres

Wrth edrych ar bethau dan feicrosgop, mae gollwng trydanol statig yn achosi problemau strwycturaidd mewn tri ffordd brif. Yn achos MOSFETs, y digwyddiad ariannir yw toriadau o ocsid y gafael. Yn sylfaenol, mae'r gollwng yn torri trwy'r haenau insyliad rhagorol tân hynny. Mae hyn yn dod yn broblem fwy wrth i'r technoleg ddod yn llai na 10 nanometr, gan fod y haenau ocsid weithiau'n dim ond tua 5 i 10 atom o waddol. Yna ceir toriadau dielectrig, sydd yn golygu, yn sylfaenol, creu lwybrau cynhwysyddol anymwys o fewn cyflwrion neu arswyddion eraill, sydd fel arfer yn arwain at gylchoedd byr. Mae problem arall yn ymwneud â chamgymeriad y cysylltiad oherwydd tensiwn gwres, lle mae'r gwres gryf yn talu'r cysylltiadau rhwng y silicin a'r rhannau metel, gan newid sut mae'r transistorau'n gweithio am byth. Mwyhafrif y methiannau hynny yn dechrau â chysylltiad dynol arferol. Dim ond cerdded ar garpad yw angen i gynhyrchu tua 1.5 cilovolt o gais. Mae ffyrdd eraill o greu'r broblem yn cynnwys offer anghywir neu liwgarwch sydd yn gwneud y wynebau'n cynnal trydan yn rhy hawdd. Mae pa mor sensitif rywbeth yn bod yn dibynnu'n fawr ar y math o ddyfeisiad yr ydym yn ei ystyried.

- ICs isel-gwedd : Methiannau ar <100 V

- Diodau ar wahân : Yn ymddwyn fel arfer dan 2–5 kV

- Proseswyr uwch : Gallant gael eu niweidio gan ddisgyniadau is na 250 V

Strategïau Diogelu rhag ESD: O Ddyluniad Ar-Chip i Gweithredu Ar Lefel y System

Mae diogelu effeithlon rhag ESD yn gofyn ar approach cydsynhwyddol aml-haen—gan integru'r diogelwyr yn uniongyrchol i mewn i'r siliciwm tra bod eu cryfhau'n digwydd ar lefel y bwrdd a'r system. Mae'r strategaeth hon o 'amddiffyniad mewn-dywysau' yn sicrhau bod bygythiadau troswyddol yn cael eu hatal cyn iddynt gyrraedd y cylchedau sensitif.

Diogelu Ar-Chip Cyfunoedig: Diodau, SCRiau, a Pherthnodiadau Snapback

Mae strwythurau diogelu ar-chip yn cael eu ffabriwyo'n uniongyrchol i mewn i gylchedau integredig er mwyn atal digwyddiadau ESD ar lefel y piniau. Mae'r datrysiadau allweddol yn cynnwys:

- Diodau Crampio cyfeirio cyrrentau eithriadol at reilffyrdd y pwerau neu'r lluniau unwaith y bydd y gwerthiant yn mynd tu hwnt i'r therfynau diogel

- SCRs (Rectifïwyr Rheoliad Silicon) actifadu lwybrau cynhyddu is-gwrthiant yn ystod digwyddiadau cyrrent uchel trwy lachio rheoliad

- Dyfeisiau 'Snapback' defnyddio cyflwr NMOS/PMOS sydd yn newid i gyflwr is-gwerthiant, cyrrent uchel ar ôl eu rhagweithio

Mae'r elfennau hyn, sydd yn ymateb mewn nhanosecynnau, yn cyfyngu'r gwerthiant gormodol i lai na 10% o lefelau dinistriol—sydd yn hanfodol i gadw ocsidau'r gat a threfniant y cysylltiadau'n iach. Rhaid i ddylunwyr gydbwysio cryfder y diogelwch â chyflwr y capacitans parasytig yn ofalus, yn enwedig mewn rhyngwynebau uchel-cyflym (e.e. PCIe 6.0, USB4), lle gall capacitans ychwanegol distorïo integritet y signal uwchben 5 Gbps.

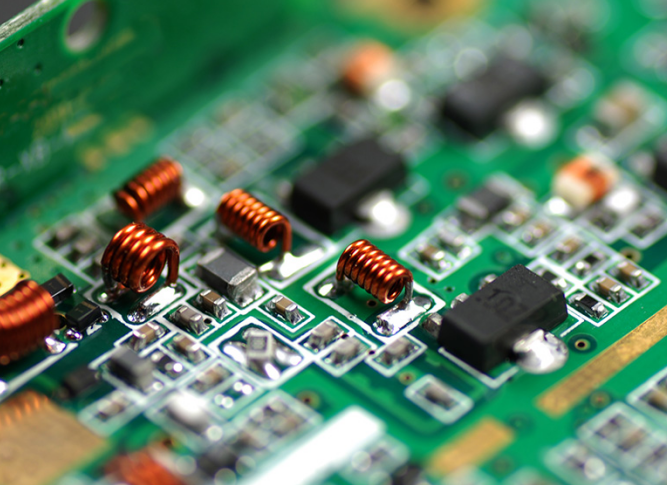

Diogelwch ESD ar lefel y system: Diôdau TVS, hidlo a chynllunio bwrdd PCB am gryfder

Mae'r diogelwch ar lefel y bwrdd yn доплментu'r amddiffyniadau ar y sipsyn drwy reoli cyrrentau eithriadol uwch-energol sydd yn mynd tu hwnt i'w meddiannau semicondŵr. Mae'r elfennau hanfodol yn cynnwys:

- Diôdau TVS (Gwahaniaethu Gwerthiant Eithriadol) : Gosodwyd o fewn 2 mm o gysylltwyr I/O i gipio'r pwyntiau tanwydd islaw 5 V mewn llai na 1 ns

- hidrolyddion Π : Cyfuno sylweddau haearnferrog a chynhwysyddion datgyswllt i leihau sŵn ESD uchel-amlder (>100 MHz)

-

Ymarfer gorau ar gyfer trefnu'r fwrdd PCB :

- Planiau tir parhaus â chynghrair isel (<15 mΩ)

- Hyd llwybr lleiaf rhwng dyfeisiau TVS ac ICs sydd dan eu hamddiffyn

- Rhannu strategol adranau analog, digidol a RF i atal cydymffurfiad

Pan fydd y mesurau hyn yn cael eu gweithredu yn henlin canllawiau IEC 61000-4-2, gallant uwchuogi'r wrthsefylliad ESD ar lefel y system gan 4–8 kV. Mae'r cynlluniau mwyaf cryf yn integru cipio TVS â thrin rhaglen wedi'i optimeiddio er mwyn sefydlu lwybrau dadgylch gynhyrchiad rhagadwy â chynghrair isel—cyfarwyddo'r ynni i ffwrdd o nodau sensitif.

Pacio a Llawdriniaeth Gwarchodol ESD ar gyfer Cyfanrwydd Cydran

Mae cadw'r cydrannau'n gyfan gwbl trwy'r broses gyfan o gynhyrchu'r wafrau tan eu defnydd terfynol yn gofyn am reoliad cryf ar sut y maen nhw'n cael eu pacio a'u hanrhydedd. Mae sawl materiel allweddol yn cael eu defnyddio at y diben hwn. Mae ffoliau sydd yn diddorwyr statig yn helpu gwarantu'r rhagor o gwrdd ar wyneb y cydrannau gan eu bod yn cynnwys lefelau gwrthiant rhwng 10^4 a 10^11 ohm. Mae treci cynhwysol a wnaed o bolymerau llwyo â charbon yn cynnal a chyflwyno unrhyw gurrentau trydar allanol. Ac yna ceir y cynhwysyddion metallig rhaglifog sydd yn creu sawl haen o ddiogelwch yn erbyn meysydd trydar allanol. Pan mae rhannau'n cael eu symud, mae cynhalwyr cydrannau arbennig yn cadw popeth yn ei le fel na fydd unrhyw beth yn cael ei anafu wrth drosglwyddo. Mae gweithrediadau logisteg hefyd yn elwa o baleidi ESD sydd yn sicrhau nad yw'r effaith triboelectrig anhebygol hon — lle mae rhai pethau'n creu trydar statig yn unig drwy gwrdd â'i gilydd — yn digwydd.

Mae'r pethau allweddol y mae pobl angen dilyn wrth drin cydrannau sensitif yn cynnwys sicrhau bod aelodau'r staff wedi'u llunio gan ddefnyddio'r llinellau gwallt sydd yn cael eu profi pob dydd, gosod ioneddwyr o amgylch arwynebau gwaith i ddileu unrhyw gwrwedd statig sydd wedi gorffen, a rhoi'r rhagwyddion rhybudd safonol hynny yn ym mhob man—fel arfer y trionglau melyn ar baciau sydd yn adnabyddadwy i bawb. Gyda'i gilydd, mae'r gosodiad hwn yn cadw lefelau trydan statig islaw 100 volt. Mae ymchwil yr diwydiant yn dangos bod cadw'r lefel hon yn lleihau rhywbeth a elwir yn 'symudiad parametrig', sef y nod sylfaenol fod damwain ESD cudd yn digwydd. Yn ôl adroddiadau amrywiol o'r sectorau cynhyrchu, awgryma'r astudiau hyn fod y fath problemau'n gallu cael eu lleihau gan fwy na 30 y cant.