主要な電気的定格値:VRMS、VRRM、IF(AV)、およびIOの解説

ピーク逆電圧(VRRM)がAC入力のピーク値を超える必要がある理由——単にVRMSを超えるだけでは不十分な理由

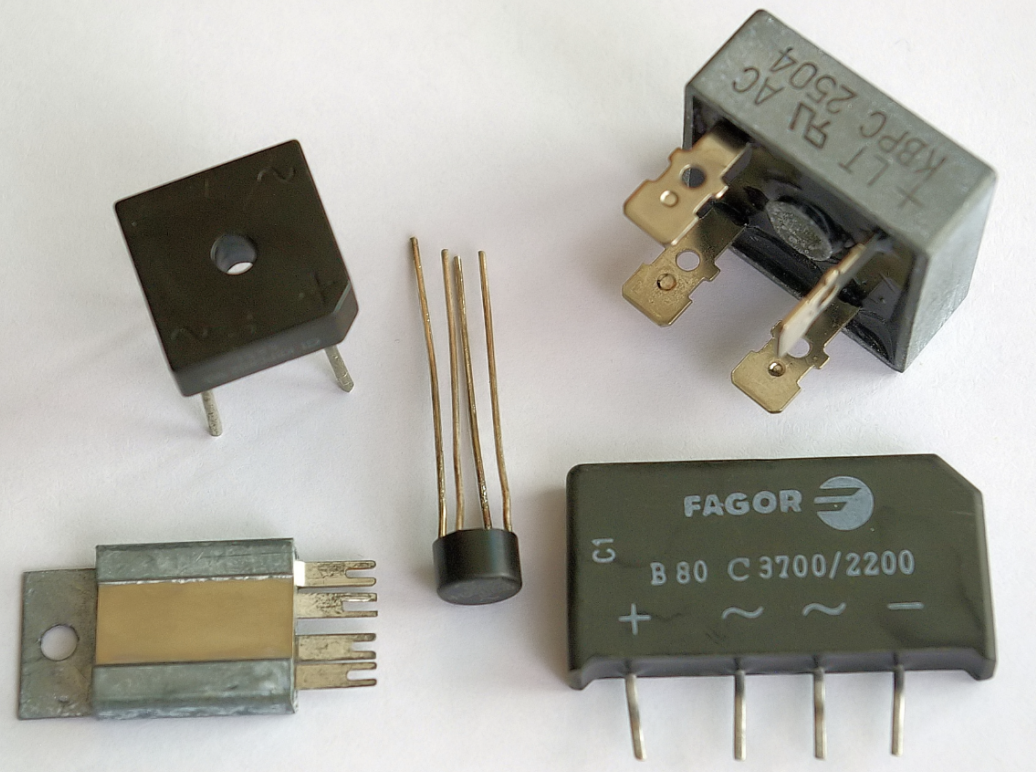

ブリッジ・レクチファイアを選定する際に、実効値電圧(VRMS)のみを基準にするのは、将来的にトラブルを招く危険性があります。実際には、交流(AC)電源ラインの電圧は、実効値で測定される値よりもはるかに高いピーク電圧に達します。たとえば、標準的な120V交流電源の場合、交流波形の数学的性質(√2 × VRMS)により、約170Vのピーク電圧に達します。ここで最も重要なのは「VRRM」(最大反復ピーク逆電圧)というパラメータであり、これは内部のダイオードが完全に破損する前に耐えられる最大逆電圧を示します。この定格値が実際の入力電圧のピーク値を下回ると、予期しない電圧サージや回路内を反射する電気ノイズなど、さまざまな問題が発生します。経験豊富なエンジニアの多くは、予測不能な条件への余裕を持たせるため、これらのピーク値に対して少なくとも1.5倍以上の定格を持つ部品を選定することを推奨しています。一般家庭用の120Vシステムでは、国際安全規格IEC 62368-1などの要件に基づき、255Vを超える定格値を目指す必要があります。

デューティサイクル、周囲温度、過渡負荷に対するIF(AV)およびIOの降格(デレーティング)

平均順方向電流(IF(AV))およびサージ電流(IO)の定格値は、理想的な実験室条件(周囲温度25°C、定常負荷)を前提としています。実際の運用では、厳格なデレーティングが求められます。

- 温度 :接合部温度の上昇により、電流容量が直接低下します。周囲温度100°Cでは、データシート仕様値と比較してIF(AV)が40%程度低下する場合があります。

- 作業サイクル :モータ起動などの間欠的高電流イベントについては、IOのパルス幅および繰返し周波数の制限に対して検証を行う必要があります。

-

過渡現象 :コンデンサのインラッシュ電流はしばしばIOを上回ります。NTCサーミスタや直列接続の電流制限抵抗器を用いて対策してください。

信頼性を確保するためには、単に目立つ定格値(ヘッドライン値)ではなく、必ず熱デレーティング曲線および過渡パルス定格値を相互参照してください。

熱性能および実環境における冷却要件

接合部から周囲への熱抵抗(R θJA ) 対実際のPCBレイアウト:銅箔面積、トレース幅、および熱伝導ビア

データシート R θJA 値は理想化された試験条件(通常、強制空冷を伴う単層基板上の大きな銅パッド)を前提としています。実際には、熱性能はPCBの実装方法によって決まります。

- 整流器直下の銅箔面積を2倍にすると、接合部温度を15–20°C低減できます。

- 狭いトレースは熱的ボトルネックとなり得るため、大電流経路には1.5 mm以上のトレース幅が推奨されます。

- パッケージ直下に配置された熱伝導ビア(≥8本/cm²、充填またはメッキ済み)により、内部層やグラウンドプレーンへの熱伝達が促進され、熱抵抗を最大40%低減できます。

周囲温度が50°Cを超えると、強制空冷が必須となります。これは、定格限界を超えて温度が10°C上昇するごとに、部品の寿命が半減する(アレニウスモデルによる)ためです。密閉型筐体や高所環境への設置では、対流効率の低下により、定格出力の30~50%を降格(デレーティング)する必要があります。早期劣化を防ぐためには、熱シミュレーションツールを用いた設計検証が不可欠です。特に、銅箔厚さを2oz以上とすること、密度を最適化すること、および低熱抵抗のヒートシンク接合界面を採用することを優先してください。楽観的な信頼性(R)評価に隠された早期故障を回避するためにも、これらの対策が重要です。 θJA フィギュア。

ブリッジ整流器のデータシートで避けるべき落とし穴

『典型的』順方向電圧という誤謬:なぜV F が高電流I F において予期せぬ損失と発熱を引き起こすのか

多くのデータシートでは、「典型的」と称される順方向電圧(V F )の測定値が、25°Cの環境温度で極めて小さな試験電流を用いて記載されています。しかし、この測定方法は、実際の負荷電流および温度変化に伴ってV F がいかに大きく変動するかという事実を隠してしまいます。部品が最大定格電流(I F )、順方向電圧は、仕様書に記載された値よりも0.2~0.4V程度急激に上昇することがよくあります。このわずかな上昇により、導通損失が著しく増加し、場合によっては20~30%にも達することがあります。たとえば、5Aの電流において順方向電圧が0.2V上昇した場合、設計計算では想定されていなかった1Wの余分な熱が発生します。その結果、設計者は部品の定格を引き下げるか、あるいは追加の冷却対策を講じる必要があります。トップメーカーでは、実際のスイッチング状況により近いパルス条件でV F を測定していますが、多くのエンジニアは依然として室温で測定された静的仕様書のみを参照しています。このような不一致は、後工程で深刻な問題を引き起こします。特に、ピーク負荷時の実際の放熱量に対してヒートシンクの能力が不足していることが判明した場合です。

高周波SMPSにおける逆回復時間(t ロープ )の無視がEMIおよび効率に与える影響

逆回復時間(t ロープ )は、スイッチング電源(SMPS)におけるスイッチング損失および電磁妨害(EMI)の両方に大きな影響を与えます。標準整流素子のt ロープ 値が500ナノ秒を超える場合、オフ時に顕著な電流リングが発生します。このリング現象は寄生LC回路を励起し、主スイッチング周波数の整数倍の周波数で広帯域のEMIを生成します。昨年IEEE EMC協会が発表した最近の研究によると、これらの影響により、システムのノイズレベルが12デシベルからほぼ18デシベルまで上昇し、再生時のエネルギー損失によって全体効率が約3%から8%程度低下するとのことです。100キロヘルツを超える周波数で動作する現代のSMPS設計では、t ロープ 値が100ナノ秒未満の超高速ダイオードが必要です。残念ながら、多くの部品仕様書には、t ロープ 温度や順方向電流の変化に伴って変動します。この欠落データは、発熱が問題となる小型パワーサプライにおいて特に深刻です。なぜなら、ダイ温度が高くなると、そもそも回復特性が悪化する傾向があるためです。

システムレベルでの統合:フィルタリング、レイアウト、信頼性の相乗効果

ブリッジ整流器の性能は、そのデータシート仕様をはるかに超えて広がっています。実効的な統合には、フィルタリング、物理的レイアウト、および熱伝導経路を調和させ、実環境下におけるストレスに対しても安定性を確保することが不可欠です。主な検討事項は以下のとおりです:

-

フィルタリングの相乗効果 :ACリップルの減衰は、バルク容量のみならず、コンデンサの種類(低ESR電解コンデンサまたはポリマー系コンデンサ)、整流器への配置距離、および整流器の動的インピーダンス特性とのインピーダンスマッチングにも依存します。不適切なフィルタリング実装は、後段のレギュレータへの負荷を増大させ、伝導性EMIを増幅させます。

-

レイアウト主導型信頼性 トランスフォーマーの二次側、整流器入力、およびバルクコンデンサによって形成されるACループ面積を最小化することで、ダイオードの信頼性を脅かす誘導性電圧スパイクを抑制します。整流器直下への戦略的な銅箔敷き(コッパーパワー)および高密度のサーマルビアにより、実効熱抵抗θが低減されます。 JAまた、高dv/dtノード間の適切な間隔確保により、容量結合によるノイズを低減します。

-

熱・電気的連成 ダイ温度の上昇によりV F が増加し、導通損失が増大します。これによりさらに発熱が促進され、正のフィードバックループが形成されます。このループはデバイスの劣化を加速させ、熱暴走のリスクを高めます。冷却対策は、瞬時電力損失だけでなく、周囲温度の上昇、隣接する発熱源、および長期的な経年劣化効果も考慮に入れる必要があります。

これらの相互依存関係を無視すると、堅牢なブリッジ整流器を用いていても、早期の故障リスクが生じます。検証済みのフィルタリング効果、低インダクタンス配線、および熱的に検証済みのレイアウトに基づく能動的な設計により、単体の部品が、現場で実証済みの耐障害性を備えた電力変換ステージへと進化します。