ESD 보호 다이오드의 작동 원리, 등가 회로, 주요 매개변수 및 선택 팁을 탐색합니다. USB, HDMI 및 전원 입력 인터페이스 보호를 위해 설계되었으며, IEC 61000-4-2에 따라 ±8kV ESD 서지 억제가 가능하여 시스템 신뢰성을 보장합니다.

정전기 방전(ESD)은 전하가 있는 물체 간의 전위 차로 인해 짧은 시간 내에 전기적 충전이 방출되는 현상입니다. 이는 정밀 전자 장치에 복구할 수 없는 손상을 줄 수 있습니다. 전자 장치가 고속화와 소형화로 계속 발전함에 따라 ESD 보호에 대한 요구사항도 더욱 엄격해지고 있습니다. ESD 보호 다이오드는 효율적이고 신뢰성 있는 보호 구성 요소로서, 신호 인터페이스 및 전원 입력과 같은 중요한 지점에서 널리 사용됩니다.

1. ESD 보호 다이오드의 기본 작동 원리

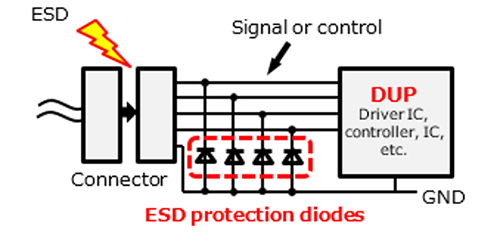

ESD 보호 다이오드는 일반적으로 역방향 바이어스된 PN 접합으로 구성됩니다. 그 핵심 메커니즘은 다이오드의 피복 특성을 이용하여 외부에서 높은 전압(예: ESD 서지)이 가해질 때 과전류를 빠르게 지면으로 유도하여 하류 구성 요소의 손상을 방지합니다.

정상 작동: 신호 라인 전압 (V 포함됨 )이 0에서 최대 역작동 전압 (V RWM ) 범위 내에 있을 때, 다이오드는 꺼져 있으며结전용(CT)처럼 동작합니다.

과전압 도통: 전압이 피크 반전 전압 (V Z 다이오드는 역방향 파괴 모드에 진입하여 전류를 흐르게 하고 특정 수준의 전압(V로 고정합니다. C ) 부하를 보호하기 위해

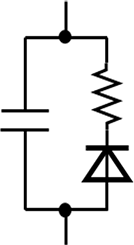

전도 상태에서 ESD 보호 다이오드는 클램핑 전압 소스와 동적 저항(R로 모델링될 수 있습니다. DYN ). 그 클램핑 성능은 내부 구조와 밀접한 관련이 있습니다.

(도면: ESD 보호 다이오드 연결 예시)

(도면: ESD 보호 다이오드의 등가 회로)

2. 주요 전기적 매개변수 분석

V RWM (최대 역작동 전압): 장치가 도통하지 않고 작동할 수 있는 최고 역전압.

V Z (파괴 전압): 장치가 역방향으로 도통하기 시작하는 최소 전압으로, 이는 그 응답 임계값을 결정합니다.

V C (클램핑 전압): 특정 전류에서 장치가 도전할 때의 전압으로, 보호의 강도를 직접 반영합니다.

R DYN (동적 저항): 도전 시 내부 저항으로, 전압 강하에 영향을 미칩니다. 더 낮은 값이 선호됩니다.

CT (접합 용량): 오프 상태에서 나타나는寄생 용량으로, 고속 신호의 무결성에 영향을 미치며 최소화되어야 합니다.

3. 동작 중인 동등 회로 모델

ESD 다이오드는 두 가지典型的한 동작 상태를 가지고 있습니다:

일반적인 조건에서 장치는 작은 커패시터처럼 동작하며, 주로 고주파 성능에 영향을 미칩니다.

ESD 서지가 발생하면 다이오드는 급속히 전도 모드로 전환되어 등가 직렬 저항과 전압 소스로 구성된 클램핑 경로를 형성합니다.

실제로 ESD 전압은 매우 가파른 상승 에지(<1 ns)를 가지고 있습니다. 이때 PCB 트레이스의 기생 인덕턴스와 커패시턴스도 보호 효과에 영향을 줄 수 있습니다. 따라서 레이아웃 최적화가 필요합니다.

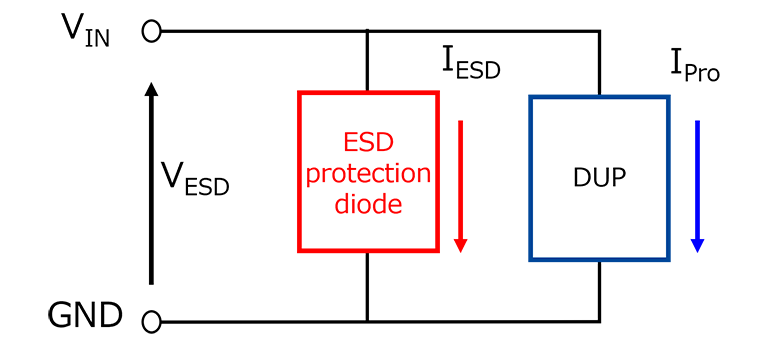

4. ESD 서지 응답 분석

8kV의 ESD 이벤트가 인터페이스에 적용된다고 가정합시다. IEC 61000-4-2에 따르면 서지 전류는 최대 30A에 도달할 수 있습니다. 다이오드의 동적 저항이 0.5Ω인 경우 일시적인 전압 강하량은 15V가 되며, 이는 클램핑 전압에 추가됩니다. 따라서 총 클램핑 전압을 줄이고 보호 대상 장치(DUP)의 전기적 스트레스를 최소화하기 위해 낮은 RDYN과 낮은 VC를 갖는 장치 선택이 중요합니다.

5. 회로 배치 및 선택 권장 사항

ESD 보호 설계에서 장치 자체의 매개변수 외에도 PCB 배치가 중요한 역할을 합니다. 다음 원칙을 준수해야 합니다:

외부 커넥터에 가능한 가까이 ESD 보호 장치를 배치하여 트레이스의寄생 인덕턴스와 전용량을 줄입니다.

지상 핀을 직접 큰 지상 면에 연결하여 인덕티브 루프를 방지합니다.

USB 3.0 또는 HDMI와 같은 고주파 인터페이스에는 저 용량 모델(예: CT ≤ 0.5pF)을 사용하는 것이 권장됩니다.

다중 채널 보호를 위해 TVS 어레이나 통합 보호 모듈의 사용을 고려하십시오.

(도표: ESD 서지 동안 간단한 회로 구성)

6. ESD 테스트 표준 개요

일반적인 ESD 내성 테스트 표준에는 다음이 포함됩니다:

IEC 61000-4-2: 시스템 수준의 ESD 내성 테스트 표준으로, 인체 방전 모델을 시뮬레이션함; 일반적인 테스트 레벨에는 ±4kV 및 ±8kV가 포함됨.

JEDEC JESD22-A114: 칩 레벨에서의 Human Body Model (HBM) 테스트 표준.

MIL-STD-883: 구성 요소의 ESD 저항을 평가하기 위한 군사 표준.

ANSI/ESD S20.20: 생산 공정 및 환경 제어를 포함하여 ESD 제어 시스템을 설정하기 위한 표준.

7. 결론

ESD 보호 다이오드는 현대 전자 제품 설계에서 ESD 이벤트에 신속하게 반응하고 일시적인 전압을 클램핑함으로써 필수적인 역할을 합니다. ESD 보호 장치를 선택할 때는 응답 속도, 클램핑 전압, 동적 저항 및结합 용량을 고려해야 합니다. 또한 최적의 보호 성능을 달성하기 위해 특정 시스템 인터페이스에 기반한 적절한 배치와 PCB 레이아웃도 중요합니다.