Jelajahi prinsip kerja, litar setara, parameter utama, dan petua pemilihan untuk diod pelindung ESD. Dikhaskan untuk perlindungan antara muka input USB, HDMI, dan kuasa, mampu menekan lonjakan ESD ±8kV mengikut IEC 61000-4-2 untuk memastikan kebolehpercayaan sistem.

Pelepasan Elektrostatik (ESD) adalah fenomena di mana cas elektrik dikeluarkan dalam tempoh masa yang singkat disebabkan perbezaan keupayaan di antara objek-objek ber cas. Ia boleh menyebabkan kerosakan yang tidak dapat dipulih kepada peranti elektronik tepat. Sebagai peranti elektronik terus berkembang menuju kelajuan yang lebih tinggi dan miniaturisasi, keperluan untuk pelindungan ESD telah menjadi lebih ketat. Dioda pelindung ESD, sebagai komponen pelindung yang cekap dan boleh dipercayai, digunakan secara meluas pada titik-titik kritikal seperti antara muka isyarat dan input kuasa.

1. Prinsip Kerja Asas Dioda Pelindung ESD

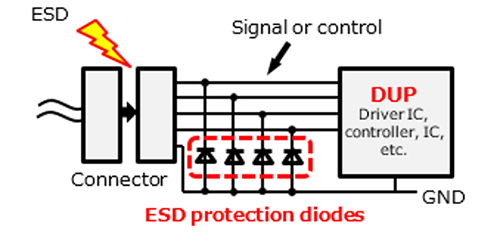

Dioda pelindung ESD biasanya terdiri daripada sambungan PN yang terbalik. Mekanisme asasnya menggunakan ciri-ciri patahan dioda untuk mengalirkan dengan pantas dan membelokkan arus berlebihan ke tanah apabila voltan tinggi, seperti lonjakan ESD, dikenakan dari luar. Ini mencegah kerosakan kepada komponen hulu.

Operasi Normal: Apabila voltan garis isyarat (V DI ) berada dalam julat 0 hingga Voltan Terus Maksimum (V RWM ), diaod tetap mati dan bertindak seperti kapasitansi sambungan (CT).

Penjanaan Voltan Lebih: Apabila voltan melampauhi Voltan Pecah (V Z ), diod memasuki mod pemecahan songsang, menghantarkan arus, dan mengekang voltan kepada tahap tertentu (V C ) untuk melindungi beban.

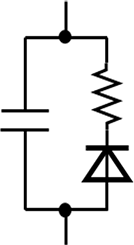

Dalam keadaan penghantaran, diod pelindung ESD boleh dimodelkan sebagai sambungan siri sumber voltan pengekang dan rintangan dinamik (R DYN ). Prestasi pengekangannya adalah berkait rapat dengan struktur dalaman ia.

(Ilustrasi: Contoh Hubungan Dioda Pelindung ESD)

(Ilustrasi: Litar Setara Dioda Pelindung ESD)

2. Analisis Parameter Elektrik Utama

V RWM (Voltan Berfungsi Songsang Maksimum): Voltan songsang tertinggi di mana peranti boleh beroperasi tanpa mengalirkan arus.

V Z (Voltan Patah Balik): Voltan minimum di mana peranti mula mengalirkan arus dalam arah songsang, menentukan ambang responnya.

V C (Voltan Penjepit): Voltan di seluruh peranti semasa penghantaran pada arus yang ditentukan, yang secara langsung mencerminkan kekuatan perlindungan.

R DYN (Rintangan Dinamik): Rintangan dalaman semasa penghantaran, yang mempengaruhi penurunan voltan. Nilai yang lebih rendah adalah yang dipilih.

CT (Kapasitans Sambungan): Kapasitans parasit yang dipamerkan dalam keadaan mati, yang mempengaruhi integriti isyarat laju tinggi dan harus dikurangkan.

3. Model Litar Setara Dalam Operasi

Diod ESD mempunyai dua keadaan operasi tipikal:

Semasa keadaan normal, peranti itu bertindak seperti kapasitor kecil, terutamanya mempengaruhi prestasi frekuensi tinggi.

Apabila lonjakan ESD berlaku, dioda menukar kepada mod pengondusian dengan pantas, membentuk laluan pengekalan yang terdiri daripada rintangan siri setara dan sumber voltan.

Dalam amalan, voltan ESD mempunyai tepi menanjak yang sangat curam (<1 ns). Pada masa ini, induktans parasit dan kapasitans trek PCB juga boleh mempengaruhi keberkesanan perlindungan. Oleh itu, penyemakan tata letak adalah perlu.

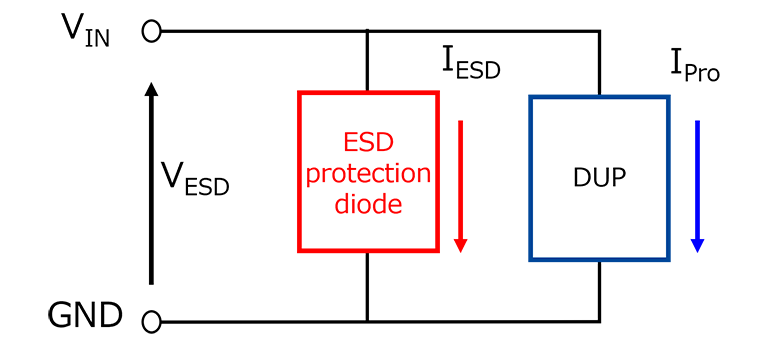

4. Analisis Tanggapan Lonjakan ESD

Anggap satu peristiwa ESD 8kV diterapkan pada antaramuka. Menurut IEC 61000-4-2, arus lonjakan boleh mencapai sehingga 30A. Jika doida mempunyai rintangan dinamik 0.5Ω, jatuh voltan sementara akan menjadi 15V, yang ditambah kepada voltan pengekalan. Oleh itu, pemilihan peranti dengan RDYN rendah dan VC rendah adalah penting untuk mengurangkan voltan pengekalan keseluruhan dan meminimumkan tekanan elektrik pada peranti yang dilindungi (DUP).

5. Tata Letak Aplikasi dan Cadangan Pemilihan

Dalam reka bentuk perlindungan ESD, selain parameter peranti itu sendiri, tata letak PCB memainkan peranan penting. Prinsip berikut harus dipatuhi:

Letakkan peranti pelindung ESD seberapa dekat mungkin dengan pengehubung luaran untuk mengurangkan induktans parasit dan kapasitans dalam trek.

Sambungkan pin tanah terus kepada satah tanah besar untuk mengelakkan gelung induktif.

Untuk antara muka frekuensi tinggi seperti USB 3.0 atau HDMI, model kapasitans rendah (contohnya, CT ≤ 0.5pF) disyorkan.

Untuk perlindungan multi-saluran, pertimbangkan penggunaan susunan TVS atau modul perlindungan terpadu.

(Ilustrasi: Konfigurasi Litar Mudah Semasa Lonjakan ESD)

6. Gambaran Keseluruhan Piawai Ujian ESD

Piawai ujian ketahanan ESD yang biasa termasuk:

IEC 61000-4-2: Piawai ujian ketahanan ESD peringkat sistem yang mensimulasikan model pelepasan badan manusia; tahap ujian tipikal termasuk ±4kV dan ±8kV.

JEDEC JESD22-A114: Piawai ujian Model Badan Manusia (HBM) pada tahap cip.

MIL-STD-883: Piawai tentera untuk menilai perlawanan ESD komponen.

ANSI/ESD S20.20: Piawai untuk membina sistem kawalan ESD, meliputi proses pengeluaran dan kawalan alam sekitar.

7. kesimpulan

Diod pelindung ESD memainkan peranan yang tidak terpisahkan dalam reka bentuk produk elektronik moden dengan merespon pantas kepada peristiwa ESD dan mengunci voltan sementara. Apabila memilih peranti pelindung ESD, seseorang harus mempertimbangkan kelajuan respon, voltan penjepit, rintangan dinamik, dan kapasitansi persimpangan. Penempatan yang betul dan susun atur PCB berdasarkan antara muka sistem tertentu juga merupakan kunci untuk mencapai prestasi perlindungan optimum.