I-explore ang prinsipyong pang-trabaho, katumbas na circuit, mga pangunahing parameter, at mga tip sa pagpili para sa ESD protection diodes. Disenyado para sa proteksyon ng USB, HDMI, at power input interface, kaya nang suprimahan ang ±8kV ESD surges ayon sa IEC 61000-4-2 upang siguruhin ang reliwablidad ng sistema.

Ang Elektrostatikong Pagpapalabas (ESD) ay isang pamamaraan kung saan inililipat ang elektrikal na bansa sa maikling panahon dahil sa pagkakaiba ng potensyal sa pagitan ng mga naka-charge na bagay. Maaaring sanhi ito ng hindi baliktad na pinsala sa mga presisong elektronikong aparato. Habang patuloy na umuunlad ang mga elektronikong device patungo sa mas mataas na bilis at miniaturisasyon, naging mas matali ang mga kinakailangan para sa proteksyon ng ESD. Bilang epektibong at tiyak na komponente ng proteksyon, madalas gamitin ang mga ESD protection diodes sa mga kritikal na punto tulad ng signal interfaces at power inputs.

1. Pangunahing Prinsipyong Paggana ng mga ESD Protection Diodes

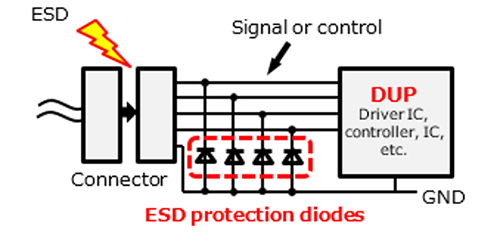

Ang mga ESD protection diodes ay karaniwang binubuo ng isang PN junction na nakareverse-bias. Ang kanilang sentral na mekanismo ay gumagamit ng characteristics ng pag-breakdown ng diode upang mabilis na mag-conduct at mag-divert ng sobrang current papunta sa lupa kapag mayroong napapanahong mataas na bansa, tulad ng isang ESD surge, na ipinapasok mula sa labas. Ito ay nagiging sanhi ng pagsisinop sa pinsala sa mga sumusunod na komponente.

Normal na Operasyon: Kapag ang voltas ng signal line (V Sa ) ay nasa sakop ng 0 hanggang sa Maximum Reverse Working Voltage (V RWM ), nananatiling off ang diyode at magiging parang kapasitansya ng junction (CT).

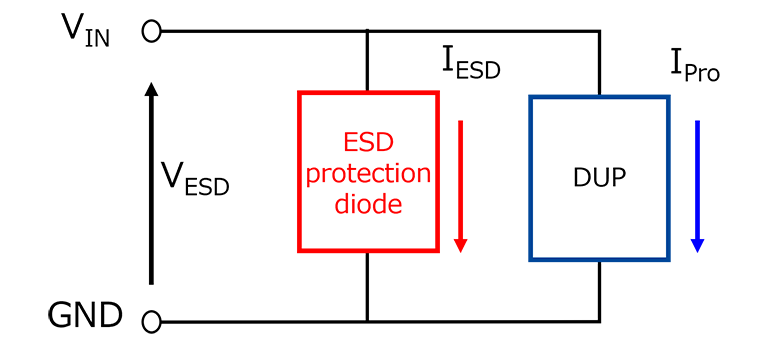

Kondukasyon sa Sobrang Voltas: Kapag ang voltas ay humigit sa Breakdown Voltage (V Z ), ang diyode ay pumapasok sa mode ng reverse breakdown, nagdadala ng kuryente, at nagclamp ng voltas sa isang tiyak na antas (V C ) upang iprotektahan ang load.

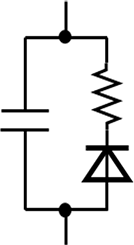

Sa estado ng pagdodulot, maaaring imodelohan ang diyode para sa proteksyon ng ESD bilang isang serye ng koneksyon ng isang voltage source na nagclamp at isang dinamikong resistensya (R DYN ). Ang kanyang pagganap sa pagclamp ay maituturing na malapit sa kanyang panloob na estraktura.

(Ilustrasyon: Halimbawa ng Paggagamit ng mga Diode para sa Proteksyon sa ESD)

(Ilustrasyon: Katumbas na Sirkwito ng Diode para sa Proteksyon sa ESD)

2. Pag-analyze ng mga Punong Elektro-Mekanikal na Parametro

V RWM (Pinakamataas na Reserve na Boltiyhe): Ang pinakamataas na reserve na voltiyhe kung saan maaaring magtrabaho ang device nang hindi umuubos.

V Z (Breakdown Voltage): Ang pinakamababang voltiyhe kung saan simulan ng device ang pag-uubos sa reserve, nagpapasiya sa kanyang threshold ng tugon.

V C (Voltage ng Pagkakasakay): Ang voltage sa device habang nasa pagpapatakbo sa isang tiyak na bilis, na direkta namamalas na proteksyon.

R DYN (Dinamikong Resistensya): Ang panloob na resistensya habang nasa pagpapatakbo, na nakakaapekto sa baba ng voltas. Mas maikling halaga ang pinapili.

CT (Junction Capacitance): Ang parasitikong kapasidad na ipinapakita sa estado ng off, na nakakaapekto sa integridad ng mabilis na senyal at dapat minimizahin.

3. Ekwiwalenteng Mga Model ng Sirkito sa Operasyon

May dalawang tipikal na estado ng operasyon ang mga ESD diode:

Sa mga normal na kondisyon, ang device ay nag-uugali tulad ng maliit na kapasitor, na pangunahing nakakaapekto sa pagganap ng mataas-na-pamalipot.

Kapag nangyayari ang isang ESD surge, ang diode ay mabilis na tumatogl sa mode ng pagdodurog, bumubuo ng isang landas ng pagdodurog na binubuo ng katumbas na serye resistensya at baterya source.

Sa praktikal na sitwasyon, ang ESD voltihi ay may napakalaking pagtaas na edge (<1 ns). Sa oras na ito, ang parasitikong induktansya at kapasitansya ng PCB traces ay maaaring mag-apekto sa epektibidad ng proteksyon. Kaya't kinakailangan ang optimisasyon ng layout.

4. Pagsusuri ng Reaksiyon sa ESD Surge

Hinihypothesize na mayroong 8kV ESD eventong inilapat sa isang interface. Ayon sa IEC 61000-4-2, maaaring umabot ang surge current hanggang 30A. Kung ang diode ay may dinamikong resistensya ng 0.5Ω, magiging 15V ang transiyenteng pagbaba ng voltihin, na idadagdag sa clamping voltage. Kaya't mahalaga ang pagsisingil ng mga device na may mababang RDYN at mababang VC upang maiwasan ang kabuuan ng clamping voltage at minimizahin ang elektrikal na stress sa pinaprotektang device (DUP).

5. Iyongak ng Aplikasyon at Mga Sugestiyon sa Piling

Sa disenyo ng proteksyon laban sa ESD, maliban sa mga parameter ng device mismo, mahalagang papel ang ginagampanan ng layout ng PCB. Dapat sundin ang mga prinsipyong ito:

Ilagay ang mga device para sa proteksyon laban sa ESD tuwing maaga malapit sa panlabas na konektor upang bawasan ang parasitikong induktansya at kapasitansya sa mga trace.

Konektahin ang mga ground pins nang diretsong patungo sa isang malaking ground plane upang iwasan ang mga inductive loop.

Para sa mataas na frekwenteng interface tulad ng USB 3.0 o HDMI, pinapalagyan ang mga modelo na may mababang kapasitansya (hal., CT ≤ 0.5pF).

Para sa multichannel na proteksyon, tingnan ang paggamit ng TVS arrays o mga integradong module ng proteksyon.

(Ilustrasyon: Simpleng Pagkakasulat ng Sirkito Sa Panahon ng ESD Surge)

6. Uri ng mga Patakaran ng Prueba para sa ESD

Mga karaniwang patakaran ng pagsubok sa resistensya sa ESD ay kasama:

IEC 61000-4-2: Patakaran sa pagsubok ng resistensya sa ESD sa antas ng sistema na nagmumula sa modelo ng pagpaputong ng katawan; mga tipikal na antas ng pagsubok ay kasama ang ±4kV at ±8kV.

JEDEC JESD22-A114: Pamantayan sa pagsubok ng Human Body Model (HBM) sa antas ng chip.

MIL-STD-883: Militer na pamantayan para sa pagsisiyasat ng ESD resistance ng mga komponente.

ANSI/ESD S20.20: Pamantayan para sa pagtatatag ng mga sistema ng ESD control, kumakatawan sa mga proseso ng produksyon at pangangalaga ng kapaligiran.

7. konklusyon

Ang mga diode para sa proteksyon ng ESD ay naglalaro ng isang mahalagang papel sa disenyo ng modernong elektronikong produkto sa pamamagitan ng mabilis na tugon sa mga kaganapan ng ESD at pagclamp ng mga transiente na voltas. Kapag pinipili ang mga device para sa proteksyon ng ESD, dapat intindihin ang bilis ng tugon, clamping voltage, dinamikong resistansya, at junction capacitance. Ang wastong paggamit at PCB layout batay sa mga espesipikong system interfaces ay pati ring mahalaga upang maabot ang pinakamahusay na pagganap ng proteksyon.