Explore o princípio de funcionamento, circuito equivalente, parâmetros-chave e dicas de seleção para diodos de proteção contra ESD. Projetado para proteção de interfaces de entrada USB, HDMI e de alimentação, capaz de suprimir surtos de ESD de ±8kV de acordo com a norma IEC 61000-4-2 para garantir a confiabilidade do sistema.

Descarga Elétrica Estática (ESD) é um fenômeno no qual a carga elétrica é liberada em um curto período de tempo devido à diferença de potencial entre objetos carregados. Ele pode causar danos irreversíveis a dispositivos eletrônicos de precisão. À medida que os dispositivos eletrônicos continuam a evoluir em direção a maior velocidade e miniaturização, os requisitos para proteção contra ESD se tornaram mais rigorosos. Diodos de proteção contra ESD, como componentes de proteção eficientes e confiáveis, são amplamente utilizados em pontos críticos, como interfaces de sinal e entradas de energia.

1. Princípio Básico de Funcionamento dos Diodos de Proteção contra ESD

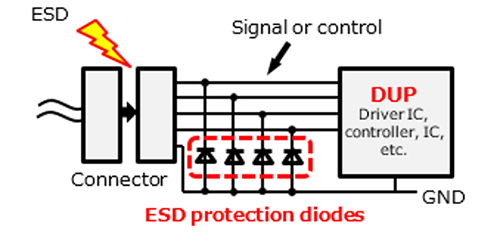

Diodos de proteção contra ESD geralmente são compostos por uma junção PN polarizada inversamente. Seu mecanismo central utiliza as características de ruptura do diodo para conduzir rapidamente e desviar correntes excessivas para a terra quando uma alta tensão, como um surto de ESD, é aplicada externamente. Isso impede danos a componentes downstream.

Operação Normal: Quando a tensão da linha de sinal (V Em ) está dentro da faixa de 0 até a Tensão Máxima de Trabalho Inverso (V RWM ), o diodo permanece desligado e se comporta como uma capacitância de junção (CT).

Condução por Sobretensão: Quando a tensão excede a Tensão de Ruptura (V Z quando a diodo entra no modo de quebra reversa, conduz corrente e fixa a tensão em um certo nível (V C ) para proteger a carga.

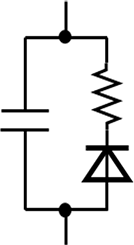

No estado de condução, o diodo de proteção ESD pode ser modelado como uma conexão em série de uma fonte de tensão de fixação e uma resistência dinâmica (R DYN ). Seu desempenho de fixação está intimamente relacionado à sua estrutura interna.

(Ilustração: Exemplo de Conexão de Diodo de Proteção contra ESD)

(Ilustração: Circuito Equivalente do Diodo de Proteção contra ESD)

2. Análise dos Parâmetros Elétricos Principais

V RWM (Tensão de Trabalho Inversa Máxima): A tensão inversa máxima na qual o dispositivo pode operar sem conduzir.

V Z (Tensão de Quebra): A tensão mínima na qual o dispositivo começa a conduzir em modo reverso, determinando seu limiar de resposta.

V C (Tensão de Atravessamento): A tensão através do dispositivo durante a condução em uma corrente especificada, que reflete diretamente a força da proteção.

R DYN (Resistência Dinâmica): A resistência interna durante a condução, afetando a queda de tensão. Preferem-se valores mais baixos.

CT (Capacitância de Junção): A capacitância parasita exibida no estado desligado, que afeta a integridade de sinais de alta velocidade e deve ser minimizada.

3. Modelos de Circuitos Equivalentes em Operação

Os diodos ESD têm dois estados típicos de operação:

Durante condições normais, o dispositivo se comporta como um capacitor pequeno, afetando principalmente o desempenho em altas frequências.

Quando ocorre uma descarga ESD, o diodo passa rapidamente para o modo de condução, formando um caminho de clamping composto por uma resistência equivalente em série e uma fonte de tensão.

Na prática, a tensão ESD tem uma borda de subida muito íngreme (<1 ns). Nesse momento, a indutância parasita e a capacitância das trilhas do PCB também podem afetar a eficácia da proteção. Portanto, a otimização do layout é necessária.

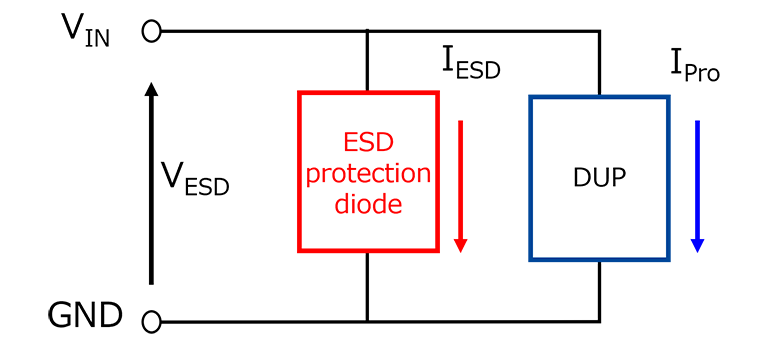

análise da Resposta à Descarga ESD

Suponha que um evento ESD de 8kV seja aplicado a uma interface. De acordo com a norma IEC 61000-4-2, a corrente de surto pode atingir até 30A. Se o diodo tiver uma resistência dinâmica de 0,5Ω, a queda de tensão transitória será de 15V, que é adicionada à tensão de clamping. Portanto, selecionar dispositivos com baixo RDYN e baixo VC é importante para reduzir a tensão total de clamping e minimizar o estresse elétrico no dispositivo protegido (DUP).

5. Layout de Aplicação e Recomendações de Seleção

No design de proteção contra ESD, além dos parâmetros do próprio dispositivo, o layout do PCB desempenha um papel crucial. Os seguintes princípios devem ser seguidos:

Posicione os dispositivos de proteção contra ESD o mais próximo possível dos conectores externos para reduzir a indutância e capacitância parasitas nas trilhas.

Conecte os pinos de terra diretamente a uma grande placa de terra para evitar laços indutivos.

Para interfaces de alta frequência como USB 3.0 ou HDMI, são recomendados modelos de baixa capacitância (por exemplo, CT ≤ 0,5pF).

Para proteção multicanal, considere usar arrays TVS ou módulos de proteção integrados.

(Ilustração: Configuração Simples de Circuito Durante Surto ESD)

6. Visão Geral dos Padrões de Teste de ESD

Padrões comuns de testes de imunidade a ESD incluem:

IEC 61000-4-2: Padrão de teste de imunidade a ESD no nível do sistema, simulando o modelo de descarga do corpo humano; níveis de teste típicos incluem ±4kV e ±8kV.

JEDEC JESD22-A114: Norma de teste do Modelo de Corpo Humano (HBM) no nível do chip.

MIL-STD-883: Padrão militar para avaliação da resistência a ESD de componentes.

ANSI/ESD S20.20: Padrão para estabelecer sistemas de controle de ESD, cobrindo processos de produção e controle ambiental.

7. conclusão

Diodos de proteção contra ESD desempenham um papel indispensável no design de produtos eletrônicos modernos ao responder rapidamente a eventos de ESD e limitar tensões transitórias. Ao selecionar dispositivos de proteção contra ESD, deve-se considerar a velocidade de resposta, a tensão de clamping, a resistência dinâmica e a capacitância de junção. A implantação adequada e o layout do PCB com base nas interfaces específicas do sistema também são fundamentais para alcançar o melhor desempenho de proteção.