Jelajahi prinsip kerja, rangkaian ekuivalen, parameter utama, dan tips pemilihan untuk dioda pelindung ESD. Dirancang untuk perlindungan antarmuka input daya, USB, dan HDMI, mampu menekan lonjakan ESD ±8kV sesuai IEC 61000-4-2 untuk memastikan keandalan sistem.

Pelepasan Statis Listrik (ESD) adalah fenomena di mana muatan listrik dilepaskan dalam waktu singkat akibat perbedaan potensial antara objek-objek yang bermuatan. Hal ini dapat menyebabkan kerusakan yang tidak dapat diperbaiki pada perangkat elektronik presisi. Seiring perkembangan perangkat elektronik menuju kecepatan lebih tinggi dan miniaturisasi, persyaratan untuk proteksi ESD telah menjadi lebih ketat. Dioda proteksi ESD, sebagai komponen pelindung yang efisien dan andal, digunakan secara luas pada titik-titik kritis seperti antarmuka sinyal dan masukan daya.

1. Prinsip Kerja Dasar Dioda Proteksi ESD

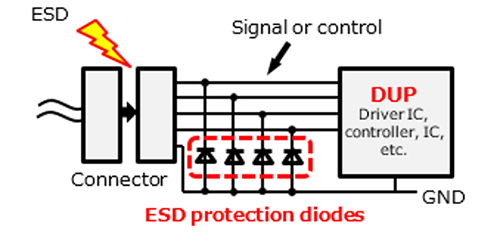

Dioda proteksi ESD umumnya terdiri dari sambungan PN yang membalikkan bias. Mekanisme inti mereka memanfaatkan karakteristik breakdown dioda untuk mengalihkan arus berlebih dengan cepat ke tanah ketika tegangan tinggi, seperti lonjakan ESD, diterapkan secara eksternal. Ini mencegah kerusakan pada komponen di hilir.

Operasi Normal: Ketika tegangan pada garis sinyal (V DI ) berada dalam rentang 0 hingga Tegangan Kerja Balik Maksimum (V RWM ), dioda tetap mati dan bertindak seperti kapasitansi sambungan (CT).

Konduksi Overvoltage: Ketika tegangan melebihi Tegangan Pemutus (V Z ), dioda memasuki mode breakdown balik, menghantarkan arus, dan menstabilkan tegangan pada tingkat tertentu (V C ) untuk melindungi beban.

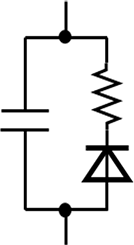

Dalam keadaan penghantaran, dioda pelindung ESD dapat dimodelkan sebagai koneksi seri dari sumber tegangan penjepit dan hambatan dinamis (R DYN ). Kinerja penjepitannya erat kaitannya dengan struktur internalnya.

(Ilustrasi: Contoh Koneksi Dioda Pelindung ESD)

(Ilustrasi: Rangkaian Setara Dioda Pelindung ESD)

2. Analisis Parameter Listrik Utama

V RWM (Tegangan Kerja Balik Maksimum): Tegangan balik maksimum di mana perangkat dapat beroperasi tanpa menghantarkan arus.

V Z (Tegangan Patahan): Tegangan minimum di mana perangkat mulai menghantarkan arus dalam keadaan balik, menentukan ambang batas responsnya.

V C (Tegangan Penjepit): Tegangan di seluruh perangkat selama konduksi pada arus tertentu, yang secara langsung mencerminkan kekuatan perlindungan.

R DYN (Hambatan Dinamis): Hambatan internal selama konduksi, memengaruhi penurunan tegangan. Nilai yang lebih rendah lebih disukai.

CT (Kapasitansi Sambungan): Kapasitansi parasit yang muncul dalam keadaan mati, yang memengaruhi integritas sinyal berkecepatan tinggi dan sebaiknya diminimalkan.

3. Model Rangkaian Setara dalam Operasi

Dioda ESD memiliki dua keadaan operasi tipikal:

Selama kondisi normal, perangkat berperilaku seperti kapasitor kecil, terutama memengaruhi kinerja frekuensi tinggi.

Ketika terjadi lonjakan ESD, dioda beralih dengan cepat ke mode konduksi, membentuk jalur penjepit yang terdiri dari hambatan seri setara dan sumber tegangan.

Dalam praktiknya, tegangan ESD memiliki tepi naik yang sangat curam (<1 ns). Pada saat ini, induktansi parasit dan kapasitansi jalur PCB juga dapat memengaruhi efektivitas perlindungan. Oleh karena itu, optimasi tata letak diperlukan.

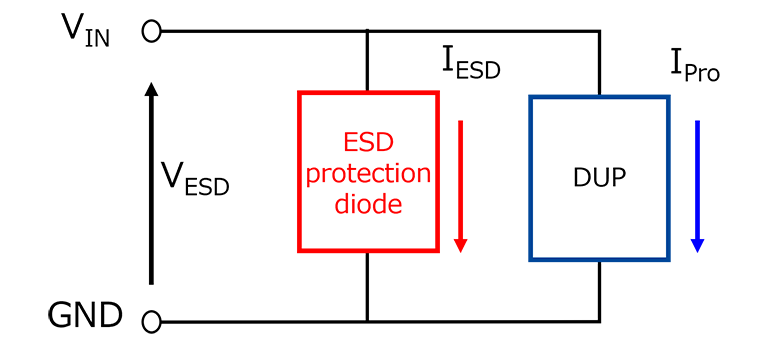

analisis Respons Lonjakan ESD

Anggap sebuah peristiwa ESD 8kV diterapkan pada antarmuka. Menurut IEC 61000-4-2, arus lonjakan dapat mencapai hingga 30A. Jika dioda memiliki hambatan dinamis 0.5Ω, penurunan tegangan sementara akan menjadi 15V, yang ditambahkan ke tegangan penjepit. Oleh karena itu, memilih perangkat dengan RDYN rendah dan VC rendah penting untuk mengurangi tegangan penjepit total dan meminimalkan stres listrik pada perangkat yang dilindungi (DUP).

5. Tata Letak Aplikasi dan Rekomendasi Pemilihan

Dalam desain pelindung ESD, selain parameter dari perangkat itu sendiri, tata letak PCB memainkan peran penting. Prinsip-prinsip berikut harus diikuti:

Letakkan perangkat pelindung ESD sedekat mungkin dengan konektor eksternal untuk mengurangi induktansi dan kapasitansi parasit dalam jejak.

Hubungkan pin tanah secara langsung ke bidang tanah besar untuk menghindari gelanggang induktif.

Untuk antarmuka frekuensi tinggi seperti USB 3.0 atau HDMI, disarankan menggunakan model dengan kapasitansi rendah (misalnya, CT ≤ 0.5pF).

Untuk perlindungan multi-channel, pertimbangkan penggunaan TVS arrays atau modul perlindungan terintegrasi.

(Ilustrasi: Konfigurasi Rangkaian Sederhana Selama Lonjakan ESD)

6. Gambaran Umum Standar Uji ESD

Standar uji kekebalan ESD yang umum meliputi:

IEC 61000-4-2: Standar pengujian kekebalan ESD pada tingkat sistem yang mensimulasikan model pembebasan tubuh manusia; tingkat uji tipikal mencakup ±4kV dan ±8kV.

JEDEC JESD22-A114: Standar pengujian Model Tubuh Manusia (HBM) pada tingkat chip.

MIL-STD-883: Standar militer untuk mengevaluasi ketahanan ESD komponen.

ANSI/ESD S20.20: Standar untuk mendirikan sistem kontrol ESD, mencakup proses produksi dan kontrol lingkungan.

7. kesimpulan

Dioda pelindung ESD memainkan peran yang tidak tergantikan dalam desain produk elektronik modern dengan merespons secara cepat terhadap peristiwa ESD dan mengunci tegangan sementara. Saat memilih perangkat pelindung ESD, harus dipertimbangkan kecepatan respon, tegangan penjepit, hambatan dinamis, dan kapasitansi sambungan. Penempatan yang tepat dan tata letak PCB berdasarkan antarmuka sistem tertentu juga merupakan kunci untuk mencapai kinerja perlindungan optimal.