Explora el principio de funcionamiento, el circuito equivalente, los parámetros clave y consejos de selección para diodos de protección contra ESD. Diseñados para la protección de interfaces de entrada USB, HDMI y de alimentación, capaces de suprimir sobretensiones de ESD de ±8kV según IEC 61000-4-2 para garantizar la fiabilidad del sistema.

La descarga electrostática (ESD) es un fenómeno en el que la carga eléctrica se libera en un corto período de tiempo debido a una diferencia de potencial entre objetos cargados. Puede causar daños irreversibles a dispositivos electrónicos de precisión. A medida que los dispositivos electrónicos continúan evolucionando hacia velocidades más altas y miniaturización, los requisitos para la protección contra ESD se han vuelto más estrictos. Los diodos de protección contra ESD, como componentes protectores eficientes y confiables, se utilizan ampliamente en puntos críticos como interfaces de señal y entradas de alimentación.

1. Principio básico de funcionamiento de los diodos de protección contra ESD

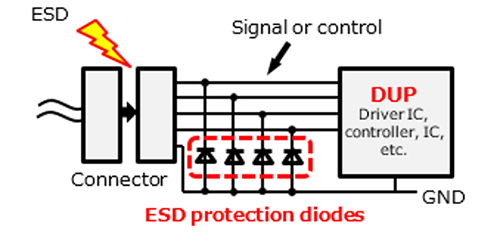

Los diodos de protección contra ESD están compuestos típicamente por una unión PN polarizada inversamente. Su mecanismo principal utiliza las características de ruptura del diodo para conducir rápidamente y desviar el sobrecorriente hacia tierra cuando se aplica un alto voltaje, como un pico de ESD, desde el exterior. Esto previene daños a los componentes downstream.

Funcionamiento Normal: Cuando la tensión de la línea de señal (V En ) está dentro del rango de 0 a la Máxima Tensión Inversa de Trabajo (V RWM ), el diodo permanece apagado y se comporta como una capacitancia de unión (CT).

Conducción Sobretensión: Cuando la tensión supera la Tensión de Rompimiento (V Z al alcanzar este valor, el diodo entra en modo de ruptura inversa, conduce corriente y fija el voltaje a un cierto nivel (V Do ) para proteger la carga.

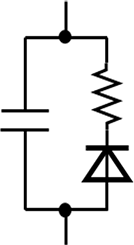

En el estado de conducción, el diodo de protección contra ESD se puede modelar como una conexión en serie de una fuente de voltaje de bloqueo y una resistencia dinámica (R DYN ). Su rendimiento de bloqueo está estrechamente relacionado con su estructura interna.

(Ilustración: Ejemplo de Conexión de Diodo de Protección contra ESD)

(Ilustración: Circuito Equivalente del Diodo de Protección contra ESD)

2. Análisis de Parámetros Eléctricos Clave

V RWM (Voltaje Máximo de Trabajo en Inversa): El voltaje inverso máximo al que el dispositivo puede operar sin conducir.

V Z (Voltaje de Quiebre): El voltaje mínimo al que el dispositivo comienza a conducir en inversa, determinando su umbral de respuesta.

V Do (Voltaje de Bloqueo): El voltaje a través del dispositivo durante la conducción a una corriente especificada, lo que refleja directamente la fuerza de la protección.

R DYN (Resistencia Dinámica): La resistencia interna durante la conducción, afectando la caída de voltaje. Se prefieren valores más bajos.

CT (Capacitancia de Unión): La capacitancia parasítica exhibida en el estado apagado, lo cual afecta la integridad de señales de alta velocidad y debe minimizarse.

3. Modelos de Circuito Equivalente en Operación

Los diodos ESD tienen dos estados típicos de operación:

Durante condiciones normales, el dispositivo se comporta como un capacitor pequeño, afectando principalmente al rendimiento de alta frecuencia.

Cuando ocurre un sobrecorriente ESD, el diodo cambia rápidamente al modo de conducción, formando una ruta de bloqueo compuesta por una resistencia equivalente en serie y una fuente de voltaje.

En la práctica, el voltaje ESD tiene un flanco de subida muy pronunciado (<1 ns). En este momento, la inductancia y capacitancia parasitarias de las trazas del PCB también pueden afectar la efectividad de la protección. Por lo tanto, es necesario optimizar el diseño del circuito.

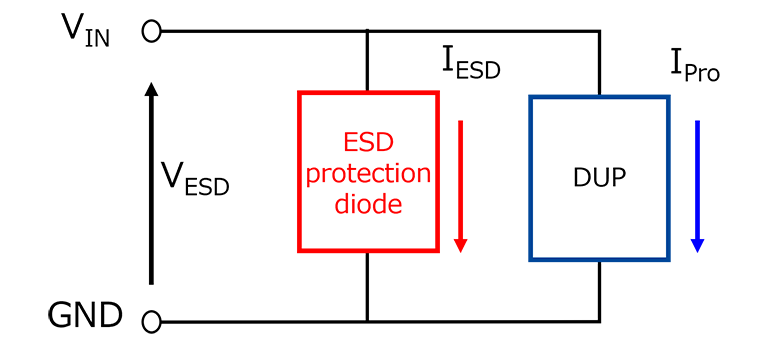

4. Análisis de la respuesta a un sobrecorriente ESD

Supongamos que un evento ESD de 8kV se aplica a una interfaz. Según la norma IEC 61000-4-2, la corriente de pico puede alcanzar hasta 30A. Si el diodo tiene una resistencia dinámica de 0.5Ω, la caída de tensión transitoria será de 15V, que se suma a la tensión de bloqueo. Por lo tanto, seleccionar dispositivos con baja RDYN y baja VC es importante para reducir la tensión total de bloqueo y minimizar el estrés eléctrico en el dispositivo protegido (DUP).

5. Diseño del Esquema y Recomendaciones de Selección

En el diseño de protección contra ESD, además de los parámetros del propio dispositivo, el diseño del PCB juega un papel crucial. Se deben seguir los siguientes principios:

Coloque los dispositivos de protección contra ESD lo más cerca posible de los conectores externos para reducir la inductancia y capacitancia parasitarias en las trazas.

Conecte las patillas a tierra directamente a un gran plano de masa para evitar bucles inductivos.

Para interfaces de alta frecuencia como USB 3.0 o HDMI, se recomiendan modelos de baja capacitancia (por ejemplo, CT ≤ 0.5pF).

Para la protección multi-canal, considere el uso de matrices TVS o módulos de protección integrados.

(Ilustración: Configuración Simple de Circuito Durante un Picazo ESD)

6. Resumen de los Estándares de Prueba de ESD

Estándares comunes de inmunidad a ESD incluyen:

IEC 61000-4-2: Estándar de prueba de inmunidad a ESD a nivel de sistema que simula el modelo de descarga del cuerpo humano; niveles de prueba típicos incluyen ±4kV y ±8kV.

JEDEC JESD22-A114: Estándar de prueba del modelo de cuerpo humano (HBM) a nivel de chip.

MIL-STD-883: Estándar militar para evaluar la resistencia a ESD de los componentes.

ANSI/ESD S20.20: Estándar para establecer sistemas de control de ESD, cubriendo procesos de producción y control ambiental.

7. conclusión

Los diodos de protección contra ESD desempeñan un papel indispensable en el diseño de productos electrónicos modernos al responder rápidamente a eventos de ESD y limitar los voltajes transitorios. Al seleccionar dispositivos de protección contra ESD, se debe considerar la velocidad de respuesta, el voltaje de bloqueo, la resistencia dinámica y la capacitancia de unión. El despliegue adecuado y el diseño del PCB basado en las interfaces del sistema específico también son claves para lograr el mejor rendimiento de protección.