Khám phá nguyên lý hoạt động, mạch tương đương, các thông số chính và lời khuyên chọn lựa cho điốt bảo vệ ESD. Thiết kế dành cho việc bảo vệ giao diện đầu vào USB, HDMI và nguồn điện, có khả năng ức chế xung ESD ±8kV theo tiêu chuẩn IEC 61000-4-2 để đảm bảo độ tin cậy của hệ thống.

Phóng điện tĩnh (ESD) là hiện tượng mà điện tích được giải phóng trong một khoảng thời gian ngắn do sự chênh lệch điện thế giữa các vật thể mang điện. Nó có thể gây ra thiệt hại không thể đảo ngược cho các thiết bị điện tử chính xác. Khi các thiết bị điện tử tiếp tục phát triển hướng tới tốc độ cao hơn và nhỏ gọn hơn, yêu cầu về bảo vệ ESD đã trở nên nghiêm ngặt hơn. Đi-ốt bảo vệ ESD, với vai trò là các thành phần bảo vệ hiệu quả và đáng tin cậy, được sử dụng rộng rãi tại các điểm then chốt như giao diện tín hiệu và đầu vào nguồn.

1. Nguyên lý cơ bản của Đi-ốt Bảo vệ ESD

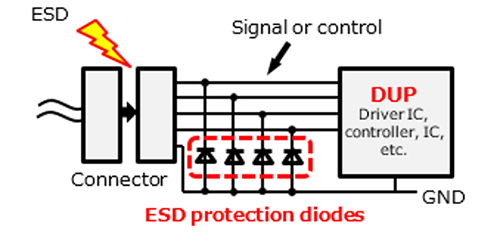

Đi-ốt bảo vệ ESD thường được cấu tạo từ một kết nối PN đảo chiều. Cơ chế cốt lõi của chúng sử dụng đặc tính phá vỡ của đi-ốt để nhanh chóng dẫn và chuyển dòng điện quá tải xuống đất khi có áp suất cao, chẳng hạn như xung ESD, tác động từ bên ngoài. Điều này ngăn ngừa thiệt hại cho các thành phần phía sau.

Hoạt động bình thường: Khi điện áp trên đường tín hiệu (V TRONG ) nằm trong phạm vi từ 0 đến Điện áp Ngược Tối đa (V RWM ), đi-ốt ở trạng thái tắt và hoạt động như một điện dung kết (CT).

Điện áp quá mức dẫn điện: Khi điện áp vượt quá Điện áp Phá vỡ (V Z khi đó, điốt chuyển sang chế độ phá vỡ ngược, dẫn điện và kẹp điện áp ở một mức nhất định (V C ) để bảo vệ tải.

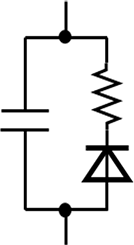

Trong trạng thái dẫn điện, điốt bảo vệ ESD có thể được mô hình hóa như một kết nối chuỗi giữa nguồn điện kẹp và một điện trở động (R DYN ). Hiệu suất kẹp của nó liên quan chặt chẽ đến cấu trúc nội bộ của nó.

(Hình minh họa: Ví dụ về kết nối Diode bảo vệ ESD)

(Hình minh họa: Mạch tương đương của Diode bảo vệ ESD)

2. Phân tích các tham số điện quan trọng

V RWM (Điện áp làm việc ngược tối đa): Điện áp ngược cao nhất mà thiết bị có thể hoạt động mà không dẫn điện.

V Z (Điện áp phá vỡ): Điện áp tối thiểu mà thiết bị bắt đầu dẫn điện ở chiều ngược, xác định ngưỡng phản hồi của nó.

V C (Điện áp kẹp): Điện áp qua thiết bị trong quá trình dẫn điện tại dòng điện đã chỉ định, phản ánh trực tiếp mức độ mạnh yếu của khả năng bảo vệ.

R DYN (Điện trở động): Điện trở nội bộ trong quá trình dẫn điện, ảnh hưởng đến sự giảm điện áp. Các giá trị thấp hơn được ưa chuộng.

CT (Điện dung结): Điện dung ký sinh xuất hiện trong trạng thái tắt, ảnh hưởng đến tính toàn vẹn của tín hiệu tốc độ cao và cần được tối thiểu hóa.

3. Mô hình mạch tương đương trong hoạt động

Các điốt ESD có hai trạng thái hoạt động điển hình:

Trong điều kiện bình thường, thiết bị hoạt động giống như một tụ điện nhỏ, chủ yếu ảnh hưởng đến hiệu suất tần số cao.

Khi xảy ra xung ESD, đi-ốt chuyển sang chế độ dẫn điện nhanh chóng, tạo thành đường dẫn kẹp gồm điện trở nối tiếp tương đương và nguồn điện áp.

Trong thực tế, điện áp ESD có biên độ dốc rất lớn (<1 ns). Lúc này, cảm kháng và điện dung ký sinh của các đường dẫn PCB cũng có thể ảnh hưởng đến hiệu quả bảo vệ. Do đó, tối ưu bố cục là cần thiết.

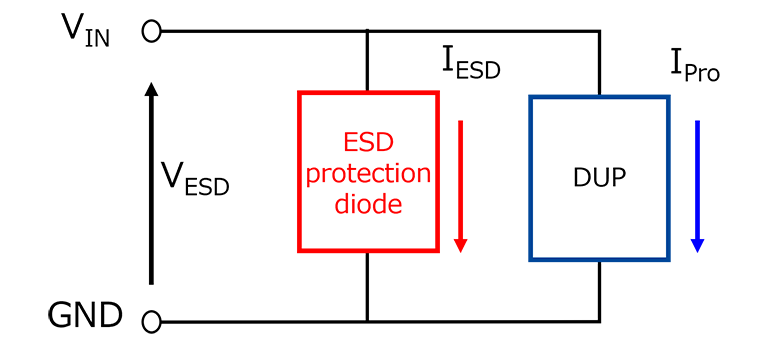

4. Phân tích phản ứng với xung ESD

Giả sử một sự kiện ESD 8kV được áp dụng vào giao diện. Theo IEC 61000-4-2, dòng xung có thể đạt tới 30A. Nếu đi-ốt có điện trở động là 0.5Ω, điện áp sụt giảm tức thời sẽ là 15V, được cộng thêm vào điện áp kẹp. Do đó, việc chọn các thiết bị có RDYN thấp và VC thấp là quan trọng để giảm tổng điện áp kẹp và tối thiểu hóa stress điện trên thiết bị được bảo vệ (DUP).

5. Bố cục ứng dụng và khuyến nghị lựa chọn

Trong thiết kế bảo vệ ESD, ngoài các thông số của thiết bị itself, bố trí PCB đóng vai trò quan trọng. Các nguyên tắc sau đây nên được tuân theo:

Đặt các thiết bị bảo vệ ESD càng gần các đầu nối bên ngoài càng tốt để giảm cảm kháng và điện dung ký sinh trong đường dẫn.

Kết nối các chân đất trực tiếp đến mặt phẳng đất lớn để tránh các vòng lặp cảm ứng.

Đối với các giao diện tần số cao như USB 3.0 hoặc HDMI, nên sử dụng các mô hình có điện dung thấp (ví dụ, CT ≤ 0.5pF).

Đối với bảo vệ đa kênh, hãy cân nhắc sử dụng mảng TVS hoặc mô-đun bảo vệ tích hợp.

( minh họa: Cấu hình mạch đơn giản trong quá trình xung ESD)

6. Tổng quan về tiêu chuẩn thử nghiệm ESD

Các tiêu chuẩn thử nghiệm khả năng chịu ESD phổ biến bao gồm:

IEC 61000-4-2: Tiêu chuẩn thử nghiệm khả năng chịu ESD cấp hệ thống mô phỏng mô hình phóng điện của cơ thể người; các mức thử nghiệm điển hình bao gồm ±4kV và ±8kV.

JEDEC JESD22-A114: Tiêu chuẩn thử nghiệm mô hình cơ thể người (HBM) ở mức chip.

MIL-STD-883: Tiêu chuẩn quân sự để đánh giá khả năng kháng ESD của các thành phần.

ANSI/ESD S20.20: Tiêu chuẩn để thiết lập hệ thống kiểm soát ESD, bao gồm các quy trình sản xuất và kiểm soát môi trường.

7. kết luận

Các điốt bảo vệ ESD đóng vai trò không thể thiếu trong thiết kế sản phẩm điện tử hiện đại bằng cách phản ứng nhanh chóng với các sự kiện ESD và kẹp điện áp tức thời. Khi chọn thiết bị bảo vệ ESD, cần xem xét tốc độ phản hồi, điện áp kẹp, điện trở động và dung kháng kết nối. Việc triển khai đúng cách và bố cục PCB dựa trên các giao diện hệ thống cụ thể cũng là chìa khóa để đạt được hiệu suất bảo vệ tối ưu.