Arwilio'r prynhawn gweithredol, y circuit cyfatebol, yr amcangyfrifon allweddol, a chyngor dewis ar gyfer diodau diogelu ESD. Dyllyd eu cynllunio ar gyfer diogelu arloesrych USB, HDMI a mewnoliadau dynameg, gan alluogi mynegi ±8kV o sgyfeilliau ESD yn unol â IEC 61000-4-2 i wneud yn siŵr cofnod system.

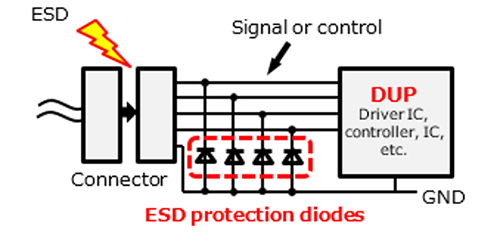

Yr ymddygiad statig (ESD) yw'r digwyddiad yng Nghyfnod rhy hir i'w herio lle cau cyfyngiant o gyfweliadau yn dilyn gwahaniaeth potensial rhwng bethau â chyfweliadau. Gall iddyn nhw achosi diweddariad anwnewidus i fysgeddau electronig precyse. Gan nad yw'r gymhariaeth ar gyfer diogyn ESD wedi bod yn llawer bach, mae'r gofynion am gymalwg ESD wedi dod yn fwy angheuol. Mae diodau diogyn ESD yn cael eu defnyddio'n sylweddol yn yr ardaloedd allweddol megis cynghorau is-signal a mynediad gref.

1. Sylfaen Gweithio Diodau Diogyn ESD

Mae diodau diogyn ESD yn cael eu cynhyrchu fel union PN yn cael eu tanio'n ôl. Mae eu mecanism cariad yn defnyddio nodweddion torri'r diod i wneud i'r amgylchedd uchelach, megis ymyrraedd ESD, gael ei dreulio i'r ddaear yn gyflym pan fydd pwrpas uwch wedi'i gymryd. Mae hyn yn atal daniodd i'r elfennau islaw.

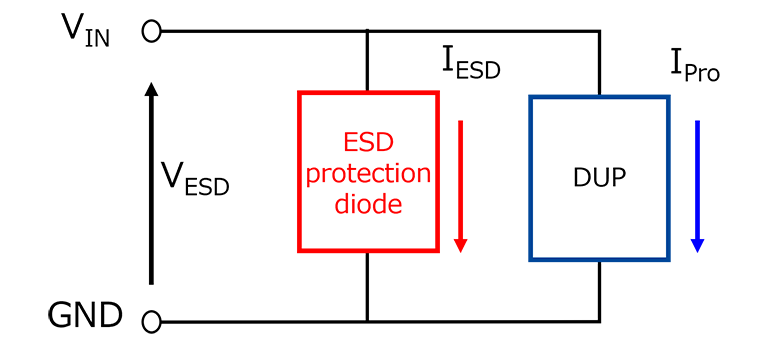

Gweithrediad Normal: Pan mae foltswydd llinell arwydd (V IN ) yn y rhan barhaol rhwng 0 i'r Foltswydd Gweithio Atgynedig Uchaf (V RWM ), aill y diod i ddod i lawr a chanlyniad fel cyfesuryn cyfuniadau (CT).

Cyflwyno Digon Ovoltaidd: Pan fydd y foltswydd yn mynd uwch na'r Foltswydd Torri (V Z ), mae'r diod yn mynd i wahanol modd torri, yn cyflwyno amheuaeth, a'n clampio'r foltiad i lefel penodol (V C ) i amddiffyn y lwyth.

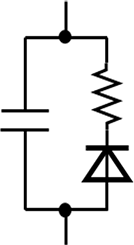

Yn y statws gyflymiant, gellir modelu'r diod amddiffyn ESD fel cyswllt o fewn o ffynhonnell foltiad clampio a chymres dyniol (R DYN ). Mae'i pherfformiad clampio yn agos ganlynol i'w strwythur mewnol.

(Delwedd: Enghraifft o Gyd-ysbennydd Diod Ddyfyniad ESD)

(Delwedd: Chwaraeon Cyfatebol ar gyfer Diod Ddyfyniad ESD)

2. Dadansoddiad Paramedrau Elecfronol Allweddol

V RWM (Ffoltiau Gwaith Ailadrodd Mai): Y ddamwain uchaf o ffoltaid ailadrodd y gall y ddisgynnwr gweithredu heb gyflwyno.

V Z (Ffoltiau Torri): Y ffoltiau isaf pan ddechreuwch y ddisgynnwr i gyflwyno'n ailadrodd, sy'n penderfyn am ei drwydded ymateb.

V C (Arwydd Amgylchedd): Yr arwydd ac mewn cyfamser yn y ddisgyn wrth gyflwyno ar gyfer amrediad penodol, sy'n adlewyrchu'n uniongyrchol y grym o'r diogelwch.

R DYN (Awstadiad Dyniol): Y rhesymau mewn cynnyrch, sy'n effeithio ar y camlofrudd foltiwg. Mae angen gofyn am werthau isel.

CT (Rhoi Cyfunydd): Y rhoi parasytig a ddangosir yn y statws i ffwrdd, sy'n effeithio ar integritas sain gyflym ac ddylid ei leiafuo.

3. Modelau Llwybr Gyda'u Gweithredu

Mae diodau ESD gydag dau statws wych o weithio:

Yn amodau cyffredin, mae'r amgylchedd yn ymddwyn fel capacitor bach, effeithio'n bennaf ar gynnydd uchel.

Pan fydd goroesi ESD yn digwydd, bydd y diod yn symud gyflym i gymod, creu llwybr clamp sy'n cael ei gymhwyso gan gyfres o dirwedd a chyfrifoldeb seriol a thrydan ffont.

Yn ymarferol, mae foltws ESD gyda rhwydr llygad sylweddol (<1 ns). Ar y pryd hwn, gall angenrhefoedd lleiaf a thrigolion PCB hefyd effeithio ar werthiant ddiogelu. Felly, mae gofrestru cynaliadwy yn hanfodol.

4. Dadansoddiad Ymateb Goroesi ESD

Cytuno eich bod wedi gwneud cais am digwyddiad ESD o 8kV i gysylltiad. O fewn IEC 61000-4-2, gall amserladd goroesi fod hyd at 30A. Os yw'r diod â chynwysiant dynodaeth o 0.5Ω, bydd y camfaniad trydan yn cael ei wneud i 15V, sy'n cael ei ychwanegu i'r foltws clamp. Felly, mae dewis amgylchedd gyda RDYN isel a VC isel yn bwysig i leihau'r foltws clamp cyfan ac i leihau stres electrichaol ar yr amgylchedd a wedi'i ddiogeluo (DUP).

5. Amrediad Arddull a Chyngor Dewisiadau

Yn y cynllunio diogyn ESD, yn ogystal â'r paramedrau o'r amgylchedd ei hun, mae arddull PCB yn chwarae rôl allweddol. Dylai'r egwyddorion canlynol gael eu dilyn:

Lleiediwch amgylcheddau diogyn ESD尽 close i gefynnogau allanol â phosibl i leihau'r arwyddocâd ffyrdd a'r cyfesurfaethau parasytig.

Cysylltwch piniau daear drwy gyfeiriad uniongyrchol at fflat daear mawr i osgoi lops inductyf.

Ar gyfer offerynnau uchel-freqnans meg USB 3.0 neu HDMI, cynigiad modelau â gyfesurfaeth isel (e.e., CT ≤ 0.5pF).

Ar gyfer amddiffyn yn llawer o sianelau, ystyried defnyddio raglenau TVS neu modiwlau amddiffynad integredig.

(Dogfen: Trefniad Cyfathrebu Syml yn Ymyl Strydoedd ESD)

6. Crynodeb ar Safonau Prawf ESD

Mae safonau cyffredinol am ddirywiad gan ESD yn cynnwys:

IEC 61000-4-2: Safon prawf dirywiad ESD ar lefel system sy'n symud delwedd llygad dyn; mewn gwahanol lefelau prawf fel ±4kV a ±8kV.

JEDEC JESD22-A114: Arferion model corff dynol (HBM) ar lefel chip.

MIL-STD-883: Arfer milwrol ar gyfer asesu dirwy ESD ar y rhanfodau.

ANSI/ESD S20.20: Arfer ar gyfer sefydlu systemau rheoli ESD, yn cynnwys brosesau cynhyrchu a chynrychiolaeth amgylcheddol.

7. Canlyniad

Mae diodau diogelu ESD yn chwarae rôl analluol yn dylunio cynnyrch electronig modern drwy ymateb gyflym i digwyddiadau ESD a thrin foltiau traedol. Dylai unigolyn cyfrifol am ymateb, foltiad clampio, atalad dynol ac atalad cysylltiad wrth dewis amgylcheddau diogelu ESD. Mae'r gwneud defnydd rhagor a lyfwyr PCB yn seiliedig ar y cyfeiriadau system penodol hefyd yn allweddol i gyrraedd perfformiad diogelus gorau.