ESDの理解:静電気放電が敏感な電子機器を損傷する仕組み

ESDの物理現象:CMOS ICにおけるゲート酸化膜の破壊とラッチアップ

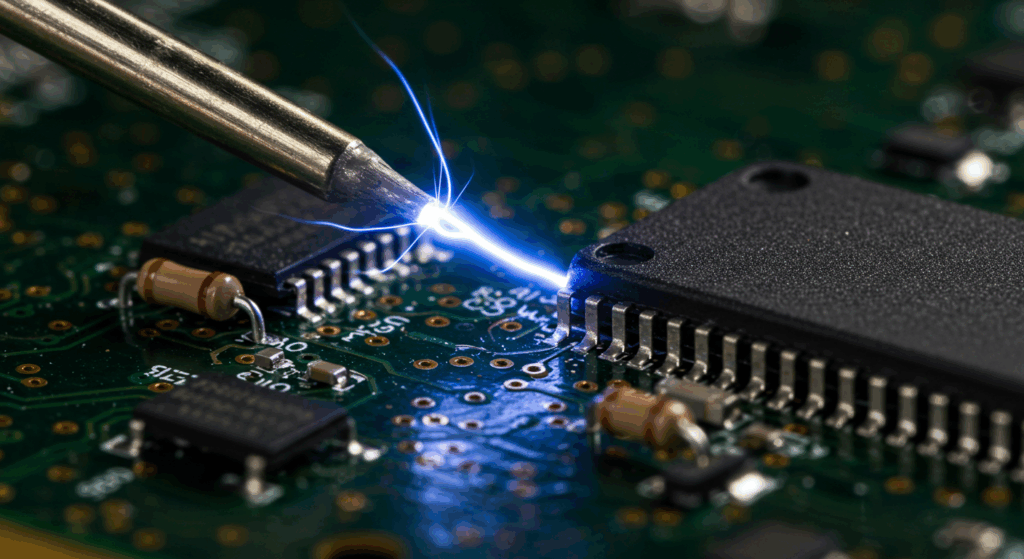

静電気放電(ESD)は、静電気が蓄積され、異なる電気的電荷を持つ物体間で突然放電する現象です。なぜこれが危険なのでしょうか?その瞬間的な電圧のサージは数千ボルトに達しますが、私たちには全く見えません。CMOSチップの場合、このエネルギーはまず最も弱い部分を攻撃します。高電圧のスパイクは非常に薄いゲート酸化膜を破壊し、トランジスタを即座に損傷させます。もう一つの問題もあります。チップ基板内に潜む厄介な寄生サイリスタ(SCR)がESDイベント中に動作を開始する可能性があるのです。これが発生すると、低抵抗パスが形成され、数アンペアにもなる破壊的な電流が自由に流れてしまいます。現代の集積回路はますます小型化され、動作電圧も低下しており、場合によっては1.2ボルト程度まで下がっています。私たちの感覚では検知できないほどのわずか100ボルト程度の電圧でも、チップを完全に破壊する可能性があります。熱モデルによれば、10アンペアを超える短時間の電流スパイクが、数十億分の一秒未満でチップ内の微細な接続部を溶融させることが明らかになっています。そのため、適切なESD保護対策は、電子機器の重大な故障を防ぐためにも、もはや単なる選択肢ではなく、絶対に不可欠なのです。

ESD損傷の種類:破壊的損傷、潜在的損傷、およびパラメータ的故障

静電気放電(ESD)は電子機器に損傷を与える際に主に3つの形で現れ、これらの問題はデバイスの経年劣化とともに徐々に悪化します。最も明らかなタイプは、テスト中に焼けた部品や溶けた金属配線など、目に見える損傷によってデバイスが即座に動作しなくなる破壊的故障です。次に、より巧妙な潜在的損傷があります。半導体接続部に微小な穴が開いたり、ゲート酸化膜が時間とともに劣化したりします。こうした問題は初期テストでは通過する場合がありますが、最終的には製品が早期に現場で故障する原因となります。業界の報告によると、隠れたESD損傷がある基板は、本来の寿命の40~60%程度しか持たないことが多いとされています。また別のカテゴリとして、完全な故障ではないが電気的特性が変化するパラメータ的故障があります。これには漏れ電流の増加や、仕様外への電圧レベルの変動が含まれ、タイミングや信号品質に悪影響を及ぼします。2023年のポンモン研究所の調査によると、破壊的故障の修復には1件あたり約5,000米ドルのコストがかかる一方、潜在的問題への対処は、原因特定に非常に多くの時間と労力を要するため、保証費用を圧迫します。優れたESD保護は、製造プロセス全体を通じて多層的な防御策を講じ、こうしたすべての状況に対応する必要があります。

| 故障タイプ | 検出ウィンドウ | 経済的影響 | 物理的現象 |

|---|---|---|---|

| 重大な故障 | 即座の | スクラップ+生産停止 | 溶融した相互接続、酸化膜の破断 |

| 潜伏的 | 数週間から数か月 | 保証請求およびリコール | 進行性の接合部劣化 |

| パラメトリック | テスト中に | 歩留まりロス+再加工 | リーク電流の増加、タイミングのずれ |

コアESD保護メカニズムおよび部品ソリューション

TVSダイオードとサージサプレッサーがESDエネルギーをどのように迂回させるか

TVSダイオードは、人体モデル試験で8kVの静電放電が発生するような場合に、過剰な電流を精密な回路から遠ざけることで、電気的サージに対する主要な防御機構として機能します。これらの部品が効果的な理由は、「低インピーダンスアバランチブレークダウン」と呼ばれるプロセスにより、電圧の急上昇に非常に迅速にクランプ(抑制)できる点にあります。これらのダイオードは、30Aもの大電流のサージを安全にグランドへ導きながら、下流の回路を許容範囲内の動作状態に保つことができます。応答時間も非常に短く、多くの場合1ナノ秒以下であり、そのためUSB 3.0ポートやHDMIケーブルなど、現代の高速接続との相性が非常に良いのです。さらに大きなエネルギーの突発的サージに対しては、多層バリスタが活用されます。これらは装置内部の金属酸化物材料中で電子が散乱するという異なるメカニズムによって、20kVを超える過渡現象から保護する機能を提供します。この能力ゆえに、極端な環境下でも損傷を防ぐ必要があるさまざまな産業分野での電源ライン保護に広く使用されています。

実際のアプリケーションにおけるクランプ電圧、応答時間、およびTLP特性

静電気放電に対する保護に関しては、基本的に最も重要な要素が3つあります。どれだけの電圧をクランプできるか、デバイスの応答速度がどのくらい速いか、そして伝送線路パルス(TLP)による試験を行ったときに何が起こるかです。クランプ電圧5ボルトで規定されたTVSダイオードを例に挙げると、このようなデバイスはゲート酸化膜が約10ボルトで破壊される傾向がある感度の高い集積回路を保護できます。5Gアンテナなどの高周波用途では、応答時間を0.5ナノ秒未満に抑えることが大きな差を生みます。そうでなければ、微細な損傷が時間とともに蓄積していく可能性があり、気づかないうちに問題が進行する恐れがあります。IEC 61000-4-2規格に準拠したTLP試験手法により、これらのデバイスがどのように故障するかを正確に把握できます。電流対電圧のプロットを確認することで、エンジニアはデバイスが急激にスナップバックするのか、それとも穏やかにクランプするのかを判断できます。メーカーが明らかにしているのは、優れたTVSダイオードは30アンペアという大電流パルス時でも動的抵抗を10オーム以下に保つことができ、高周波信号を扱う現代の電子機器においては、ポリマー系ソリューションを実際に上回る性能を発揮するということです。

ESDサプレッショントехノロジーの比較

| 構成部品 | 典型的なクランプ電圧 | 応答時間 | 最大サージ電流 | ケース |

|---|---|---|---|---|

| テレビダイオード | 3–15V | <1 ns | 30A | 高速データライン |

| 多層バリスタ | 20–600V | 5–50 ns | 70a | 電源ライン |

| ガス放電チューブ | 75–1000V | 100–500 ns | 20kA | テレコムインフラ |

クランプ精度とサージ容量のバランスを取ることは不可欠です。過剰設計ではコストが増加し、保護不足ではCMOSのラッチアップリスクが生じます。

現代エレクトロニクス向けの効果的なESD保護回路の設計

優れたESD保護回路を設計するには、サージが最初に侵入するコネクタや入出力ポートの直近に、TVSダイオードなどのサプレッション部品を配置することが重要です。クランプ電圧は、保護対象の部品を損傷させる値の直下に設定する必要があります。同時に、接合部のキャパシタンスを低く保つことで、現代のインターフェースで見られる高速データ伝送における信号品質を維持できます。PCB基板上の配線を短くすることで、トレースのインダクタンスを低減でき、必要時にシステム全体の応答性が向上します。多くのエンジニアは現在、単一の保護ポイントよりも厳しい状況に効果的に対処できる多段階の保護構成を好んで採用しています。ANSI/ESD S20.20-2021などの規格に準拠することで、製造業者は自社の製品が突然の故障や長期間にわたる徐々の劣化の両方に対して耐えうることを確信でき、安心できます。チップがナノメートルサイズまで小型化され、静電気による損傷に対して実際により脆弱になっている今日では、この点がさらに重要になっています。TLP法によるシステムレベルでの試験は依然として不可欠であり、実験室での結果が現場で発生する予期しない静電気イベントのすべてと一致しない可能性があるためです。

ESD対策済み作業環境:ワークステーションから包装まで

製造における静電気 dissipative 床材とISO 6360適合性

ESD対策が施された環境を構築するには、導電性を備えたEPDMタイルなどの適切な床材から始まります。このような床材は、表面抵抗値を100万〜10億オームの範囲内に保ち、静電気が蓄積されるのではなく安全に放散されるようにします。ISO 6360-5規格によると、施設では床の抵抗値および接地接続を定期的に測定する必要があります。2023年のERAIの調査によれば、これらのガイドラインに従っている企業は、そうでない企業と比較して静電気放電事故が約75%少なくなっています。このシステムは、床、作業台面、そして実際のアース接地との間に接地ポイントを接続することで機能します。これにより完全な回路が形成され、電子機器製造で使用される精密な集積回路にとって一般的に安全限界とされる100ボルトを超える電圧の蓄積を防ぎます。

二重遮蔽バッグとファラデーケージの原理による安全な保管

2層構造のシールド袋は、ファラデーケージの原理に基づいており、部品を保管または搬送中に安全に保護します。外側の層には金属コーティングが施されており、外部からの静電気を遮断します。一方、内側は特殊なプラスチックでできており、袋内部に蓄積された静電荷を除去する役割を果たします。これらの保護袋は、IEC規格によると、静電エネルギーを約50デシベル低減し、およそ8,000ボルト以上の放電を防止します。実際、シールの密閉状態を正しく保つことは非常に重要であり、適切に閉じられていない場合、保護性能はほぼ90%も低下してしまいます。CMOSセンサーなどの敏感な部品を扱う際には、湿度が30%以下に保たれた環境制御キャビネットに収納することで、後々発生する潜在的な問題を効果的に防ぐことができます。輸送および取り扱いの全過程においてファラデーshieldの完全性を維持することは極めて重要です。なぜなら、ほんの一瞬でも適切な保護が失われれば、それまで部品を守るために講じてきたすべての対策が無効になってしまう可能性があるからです。

よく 聞かれる 質問

静電気放電(ESD)とは何ですか?

静電気放電(ESD)は、2つの帯電した物体間に急激な電流が流れる現象であり、敏感な電子機器に損傷を与えることが多い。

なぜ電子機器において静電気放電保護が重要ですか?

ESD保護は極めて重要である。なぜなら、静電気放電は電子部品において破壊的な故障、潜在的な損傷、およびパラメータ変化を引き起こし、寿命の短縮や高額な修理費用につながる可能性があるからである。

ESDはどのようにして電子機器を損傷するのか?

ESDはCMOS IC内のゲート酸化膜を破壊したり、寄生サイリスタ(シリコン制御整流素子)を活性化させ、装置を損傷する破壊的な電流を発生させる可能性がある。

TVSダイオードとは何ですか?

TVSダイオードは、過剰な電流および電圧サージを繊細な回路から遠ざけるために使用される保護用部品であり、静電気放電による損傷を防止する。

ファラデーケージとは何か、そしてどのように電子機器を保護するのか?

ファラデーケージは、静電界および電磁界から内部の物質を遮蔽する構造体であり、電子部品を安全に保管するための包装ソリューションとしてよく使用される。