Compreendendo a ESD: Como a Descarga Eletrostática Danifica Eletrônicos Sensíveis

A Física da ESD: Ruptura do Óxido de Porta e Latch-Up em Circuitos Integrados CMOS

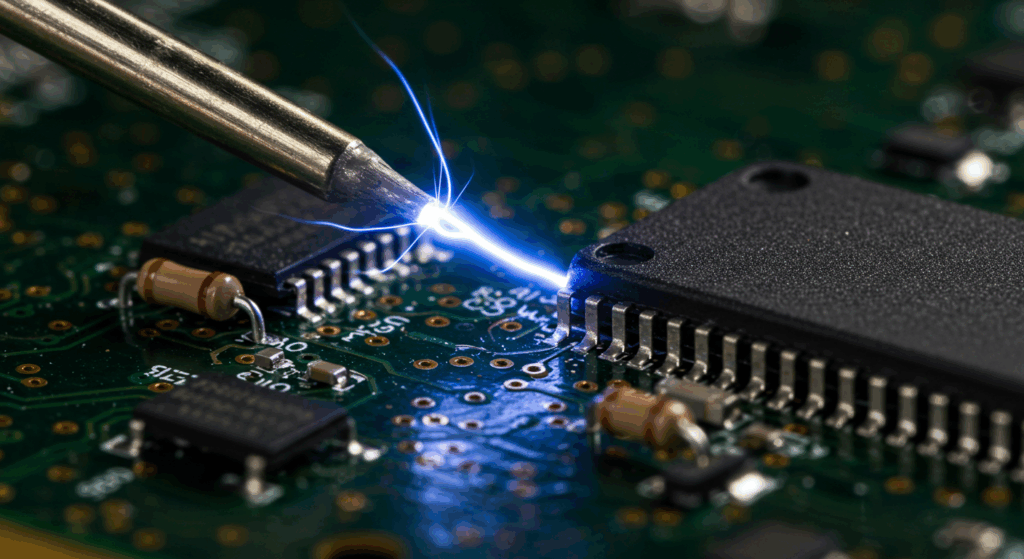

A DESC ocorre quando a eletricidade estática se acumula e depois salta entre objetos com cargas elétricas diferentes. O que a torna perigosa? Bem, esses picos súbitos de tensão atingem milhares de volts, mas não conseguimos vê-los. Para os chips CMOS, essa energia ataca primeiro os pontos mais fracos. Picos de alta tensão rompem as camadas extremamente finas de óxido de porta, o que basicamente destrói os transistores imediatamente. Há outro problema também. Os indesejáveis retificadores controlados de silício parasitas escondidos no substrato do chip podem ser ativados durante um evento de DESC. Quando isso acontece, eles criam caminhos de baixa resistência que permitem a passagem livre de correntes destrutivas, às vezes atingindo vários amperes. Os circuitos integrados modernos estão cada vez menores e operam com tensões muito mais baixas atualmente, chegando a cerca de 1,2 volt em alguns casos. Mesmo algo tão pequeno quanto 100 volts, muito abaixo do que nossos sentidos conseguem detectar, pode danificar completamente um chip. Modelos térmicos mostram que picos breves de corrente superiores a 10 amperes podem realmente derreter as minúsculas conexões internas de um chip em menos de meio bilionésimo de segundo. É por isso que a proteção adequada contra DESC não é mais apenas uma vantagem — é absolutamente essencial para evitar falhas catastróficas nos eletrônicos.

Tipos de Danos por ESD: Falhas Catastróficas, Latentes e Paramétricas

A descarga eletrostática manifesta-se de três formas principais ao danificar eletrônicos, e esses problemas pioram progressivamente conforme os dispositivos envelhecem. O tipo mais óbvio é a falha catastrófica, na qual o dispositivo basicamente para de funcionar imediatamente devido a danos visíveis, como peças queimadas ou trilhas metálicas derretidas, que podem ser observadas durante testes. Em seguida, há o dano latente, muito mais sorrateiro. Pequenos orifícios se formam nas conexões semicondutoras ou os óxidos de porta se degradam ao longo do tempo. Esses problemas podem passar pelos testes iniciais, mas acabam causando falhas precoces dos produtos em campo. Relatórios do setor indicam que placas com danos ocultos por ESD frequentemente duram apenas 40 a 60 por cento do tempo esperado. As falhas paramétricas são outra categoria, nas quais as propriedades elétricas mudam sem haver falha completa. Pense em correntes de fuga aumentadas ou níveis de tensão que saem das especificações, o que compromete o tempo de resposta e a qualidade do sinal. Corrigir falhas catastróficas custa cerca de $5.000 cada, segundo pesquisa da Ponemon de 2023, enquanto lidar com problemas latentes consome os orçamentos de garantia, pois descobrir o que deu errado exige muito tempo e esforço. Uma boa proteção contra ESD precisa abranger todos esses cenários com múltiplas camadas de defesa ao longo de todo o processo de fabricação.

| Tipo de Falha | Janela de Detecção | Impacto Financeiro | Manifestação Física |

|---|---|---|---|

| Catastrófico | Imediatamente | Sucata + paralisação da produção | Interconexões fundidas, ruptura do óxido |

| Latente | Semanas a meses | Reclamações de garantia + recalls | Degradação progressiva da junção |

| Paramétrico | Durante os testes | Perda de rendimento + retrabalho | Vazamento elevado, deriva de temporização |

Mecanismos de Proteção ESD Nucleares e Soluções por Componentes

Como os Diodos TVS e Supressores de Surtos Desviam a Energia ESD

Os diodos TVS atuam como mecanismo primário de defesa contra sobretensões elétricas, desviando a corrente excessiva de circuitos delicados quando ocorre algo como uma descarga eletrostática de 8 kV em um teste com modelo de corpo humano. O que torna esses componentes eficazes é a sua capacidade de limitar rapidamente picos de tensão graças a um processo chamado ruptura por avalanche de baixa impedância. Eles suportam sobretensões de até 30 amperes antes de encaminhá-las com segurança para o terra, mantendo ao mesmo tempo os circuitos downstream funcionando dentro dos limites aceitáveis. Os tempos de resposta também são incrivelmente rápidos, muitas vezes abaixo de um nanosegundo, o que explica seu excelente desempenho com conexões modernas de alta velocidade, como as encontradas em portas USB 3.0 ou cabos HDMI. Para situações que envolvem rajadas de energia ainda maiores, entram em ação os varistores multicamadas. Estes oferecem proteção adicional contra transientes superiores a 20 kV por meio de um mecanismo diferente, no qual os elétrons se dispersam por materiais de óxido metálico no interior do dispositivo. Devido a essa capacidade, são comumente utilizados na proteção de linhas de alimentação em diversos ambientes industriais, onde condições extremas poderiam causar danos.

Tensão de Clampagem, Tempo de Resposta e Caracterização TLP em Aplicações do Mundo Real

Quando se trata de proteção contra descargas eletrostáticas, existem basicamente três fatores mais importantes: a quantidade de tensão que é limitada, a velocidade com que o dispositivo reage e o que acontece quando o testamos com pulsos de linha de transmissão (TLP). Considere um diodo TVS com tensão de limitação de 5 volts – isso mantém os circuitos integrados sensíveis protegidos, já que o óxido de porta deles costuma se romper em torno de 10 volts. Para componentes de RF, como antenas 5G, conseguir tempos de resposta inferiores a meio nanossegundo faz realmente diferença. Caso contrário, pequenos danos podem se acumular ao longo do tempo sem que ninguém perceba. Testes com métodos TLP de acordo com as normas IEC 61000-4-2 mostram exatamente como esses dispositivos falham. Analisar gráficos de corrente versus tensão ajuda os engenheiros a identificar se o dispositivo apresenta uma ruptura abrupta ou uma limitação suave. O que os fabricantes observam é que bons diodos TVS mantêm sua resistência dinâmica abaixo de 10 ohms, mesmo durante pulsos elevados de 30 ampères. Isso supera soluções baseadas em polímeros quando se lida com sinais de alta frequência na eletrônica moderna.

Comparação de Tecnologias de Supressão de ESD

| Componente | Tensão de Clamp Típica | Tempo de resposta | Corrente de Surtos Máxima | Caso de utilização |

|---|---|---|---|---|

| Diodo de televisão | 3–15V | <1 ns | 30A | Linhas de Dados de Alta Velocidade |

| Vistor Multicamada | 20–600V | 5–50 ns | 70a | Trilhos de Alimentação Elétrica |

| Tubo de Descarga a Gás | 75–1000V | 100–500 ns | 20KA | Infraestrutura de Telecomunicações |

Equilibrar a precisão de fixação e a capacidade de sobretensão é essencial – superdimensionar aumenta o custo, enquanto uma proteção insuficiente arrisca o travamento CMOS.

Projeto de Circuitos Eficientes de Proteção contra Descargas Eletrostáticas para a Eletrônica Moderna

Para projetar bons circuitos de proteção contra ESD, é importante posicionar componentes supressores como diodos TVS bem próximos aos conectores e portas de entrada/saída, onde as sobretensões tendem a entrar primeiro, antes de atingir os circuitos integrados sensíveis. A tensão de clamp deve ser definida logo abaixo do nível que danificaria os componentes protegidos. Ao mesmo tempo, manter baixa a capacitância da junção ajuda a preservar a qualidade do sinal em transferências de dados rápidas, como nas interfaces modernas. Trajetos mais curtos na placa PCB reduzem a indutância das trilhas, fazendo com que todo o sistema responda melhor quando necessário. Muitos engenheiros agora preferem configurações de proteção em múltiplos estágios porque lidam muito melhor com situações difíceis do que soluções de ponto único. Seguir normas como a ANSI/ESD S20.20-2021 dá tranquilidade aos fabricantes, sabendo que seus produtos podem suportar tanto falhas repentinas quanto degradação lenta ao longo do tempo. Isso é ainda mais importante hoje, já que os chips estão ficando cada vez menores, alcançando tamanhos em escala nanométrica, nos quais se tornam mais vulneráveis a danos eletrostáticos. Os testes em nível de sistema com métodos TLP ainda são cruciais, pois os resultados de laboratório nem sempre correspondem ao que acontece no campo, com todos os tipos de eventos estáticos inesperados.

Ambientes de Trabalho ESD-Seguros: De Postos de Trabalho à Embalagem

Pisos Estático-Dissipativos e Conformidade com a ISO 6360 na Manufatura

Criar um ambiente seguro contra descargas eletrostáticas começa com materiais adequados para o piso, como ladrilhos de EPDM infundidos com propriedades condutivas. Esses pisos mantêm sua resistência superficial na faixa de 1 milhão a 1 bilhão de ohms, permitindo que as cargas estáticas se dissipem com segurança, em vez de se acumularem. De acordo com a norma ISO 6360-5, as instalações precisam testar regularmente a resistência do piso e as conexões de aterramento. Empresas que seguem essas diretrizes apresentaram cerca de 75% menos incidentes de descarga eletrostática do que aquelas que não estão em conformidade, segundo pesquisa realizada pela ERAI em 2023. O sistema funciona conectando pontos de aterramento entre o piso, as superfícies de trabalho e o aterramento físico. Isso cria um circuito completo que impede o acúmulo de tensão acima de 100 volts, valor geralmente considerado o limite de segurança para circuitos integrados sensíveis utilizados na fabricação de eletrônicos.

Bolsas de Blindagem em Dupla Camada e Princípios de Gaiola de Faraday para Armazenamento Seguro

Bolsas de proteção com duas camadas funcionam com base no conceito de gaiola de Faraday para manter os componentes seguros durante armazenamento ou transporte. A camada externa possui um revestimento metálico que repele qualquer eletricidade estática proveniente de fontes externas, enquanto a parte interna, feita de plástico especial, ajuda a dissipar cargas acumuladas dentro da própria bolsa. Essas bolsas protetoras reduzem os níveis de energia eletrostática em cerca de 50 decibéis, impedindo descargas superiores a aproximadamente 8.000 volts, conforme as normas IEC. O fechamento adequado é muito importante, pois, se a bolsa não for bem selada, a proteção cai quase 90 por cento. Ao lidar com itens sensíveis como sensores CMOS, colocá-los em armários com ambiente controlado, onde a umidade permanece abaixo de trinta por cento, ajuda bastante a prevenir problemas ocultos futuros. Manter a blindagem de Faraday intacta durante todo o transporte e manuseio é extremamente importante, já que um único momento sem proteção adequada pode anular todos os demais cuidados tomados para proteger essas peças valiosas.

Perguntas Frequentes

O que é Descarga Eletrostática (DE)?

A descarga eletrostática (ESD) ocorre quando há um fluxo súbito de eletricidade entre dois objetos eletricamente carregados, muitas vezes causando danos a eletrônicos sensíveis.

Por que a proteção contra ESD é importante para os equipamentos eletrônicos?

A proteção contra ESD é crucial porque a descarga eletrostática pode causar falhas catastróficas, danos latentes e alterações paramétricas em componentes eletrônicos, levando à redução da vida útil e a altos custos de reparo.

Como a ESD danifica eletrônicos?

A ESD pode romper óxidos de porta e ativar retificadores controlados de silício parasitas em circuitos integrados CMOS, causando correntes destrutivas que danificam o dispositivo.

O que são diodos TVS?

Os diodos TVS são componentes de proteção usados para desviar correntes excessivas e picos de tensão de circuitos delicados, prevenindo danos por descarga eletrostática.

O que é uma gaiola de Faraday e como ela protege eletrônicos?

Uma gaiola de Faraday é uma estrutura que protege o seu conteúdo contra campos estáticos e eletromagnéticos, sendo frequentemente usada como solução de embalagem para armazenar componentes eletrônicos com segurança.

Sumário

- Compreendendo a ESD: Como a Descarga Eletrostática Danifica Eletrônicos Sensíveis

- Mecanismos de Proteção ESD Nucleares e Soluções por Componentes

- Projeto de Circuitos Eficientes de Proteção contra Descargas Eletrostáticas para a Eletrônica Moderna

- Ambientes de Trabalho ESD-Seguros: De Postos de Trabalho à Embalagem

- Perguntas Frequentes