Memahami ESD: Bagaimana Pelepasan Elektrostatik Merosakkan Elektronik Sensitif

Fizik ESD: Kerosakan Oksida Get dan Latch-Up dalam IC CMOS

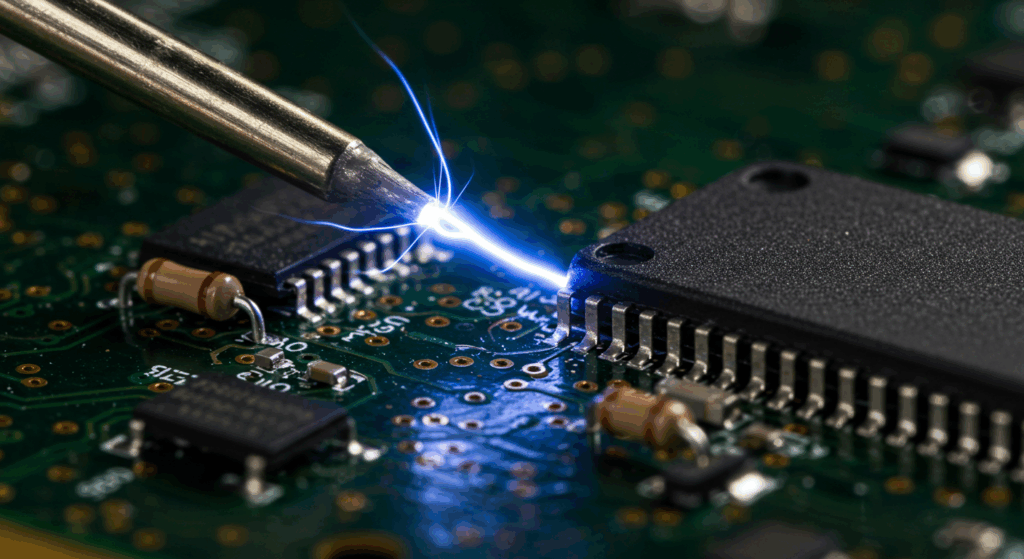

ESD berlaku apabila elektrik statik terkumpul dan kemudian melompat antara objek dengan cas elektrik yang berbeza. Apa yang menjadikannya berbahaya? Lonjakan voltan yang tiba-tiba ini diukur dalam ribuan volt, tetapi kita langsung tidak dapat melihatnya. Bagi cip CMOS, tenaga ini akan menyerang bahagian yang paling lemah terlebih dahulu. Denyutan voltan tinggi merosakkan lapisan oksida get yang sangat nipis, yang pada asasnya memusnahkan transistor serta-merta. Terdapat juga masalah lain. Rectifier terkawal silikon parasit yang sukar dikesan di dalam substrat cip mungkin aktif semasa kejadian ESD. Apabila ia berlaku, ia mencipta laluan rintangan rendah yang membenarkan arus merosakkan mengalir dengan bebas, kadangkala mencapai kuasa beberapa amp. Litar bersepadu moden kini semakin kecil dan beroperasi pada voltan yang jauh lebih rendah, sehingga kira-kira 1.2 volt dalam sesetengah kes. Malah sesuatu yang kecil seperti 100 volt, jauh di bawah tahap yang boleh dikesan oleh deria kita, boleh merosakkan cip sepenuhnya. Model terma menunjukkan bahawa denyutan arus yang melebihi 10 amp dalam tempoh singkat boleh meleburkan sambungan kecil di dalam cip dalam masa kurang daripada setengah bilion saat. Oleh itu, perlindungan ESD yang betul kini bukan sahaja baik untuk dimiliki, tetapi benar-benar penting untuk mencegah kegagalan elektronik secara teruk.

Jenis Kerosakan ESD: Kegagalan Catastrophic, Latent, dan Parametrik

Pelepasan elektrostatik muncul dalam tiga cara utama apabila merosakkan peralatan elektronik, dan masalah ini semakin teruk seiring usia peranti. Jenis yang paling ketara ialah kegagalan katasstrofik di mana peranti secara asasnya terus mati akibat kerosakan nyata seperti komponen terbakar atau laluan logam melebur yang boleh dilihat semasa ujian. Kemudian terdapat kerosakan laten yang jauh lebih licik. Lubang-lubang kecil terbentuk pada sambungan semikonduktor atau oksida getus rosak secara beransur-ansur. Isu-isu ini mungkin lulus ujian awal tetapi akhirnya menyebabkan produk gagal lebih awal di pasaran. Laporan industri menunjukkan bahawa papan litar dengan kerosakan ESD tersembunyi kerap kali hanya bertahan selama 40 hingga 60 peratus daripada jangka hayat sepatutnya. Kegagalan berparameter merupakan kategori lain di mana ciri-ciri elektrik berubah tanpa kegagalan sepenuhnya. Bayangkan arus bocor yang meningkat atau aras voltan yang berubah keluar dari spesifikasi, yang mengganggu penjajaran masa dan kualiti isyarat. Membaiki kegagalan katasstrofik biasanya menelan kos sekitar $5,000 setiap satu menurut kajian Ponemon pada tahun 2023, manakala menangani isu laten menghakis belanjawan jaminan kerana mengenal pasti punca masalah memerlukan banyak masa dan usaha. Perlindungan ESD yang baik perlu merangkumi semua senario ini dengan berbilang lapisan pertahanan sepanjang proses pengeluaran.

| Jenis Kegagalan | Tetingkap Pengesanan | Impak Kewangan | Manifestasi Fizikal |

|---|---|---|---|

| Bencana | Segera | Skrap + hentian pengeluaran | Sambungan melebur, kerosakan oksida |

| Tersembunyi | Minggu kepada bulan | Tuntutan jaminan + penarikan semula | Kerosakan simpang progresif |

| Parametrik | Semasa ujian | Kehilangan hasil + kerja semula | Kebocoran tinggi, anjakan masa |

Mekanisme Perlindungan ESD Teras dan Penyelesaian Komponen

Bagaimana Diod TVS dan Peredam Limpahan Mengalihkan Tenaga ESD

Diod TVS bertindak sebagai mekanisme pertahanan utama terhadap lompatan elektrik dengan mengalihkan arus berlebih dari litar yang sensitif apabila berlakunya descas statik 8kV seperti dalam ujian model badan manusia. Apa yang menjadikan komponen ini berkesan adalah keupayaannya untuk mencengkam lonjakan voltan dengan cepat berkat proses yang dikenali sebagai kerosakan avalanche impedans rendah. Mereka mampu mengendalikan lompatan sehingga 30 amp sebelum dihantar selamat ke bumi, sambil mengekalkan litar hiliran beroperasi dalam had yang diterima. Masa tindak balas juga sangat pantas, sering kali kurang daripada satu nanosaat, yang menjelaskan mengapa mereka berfungsi begitu baik dengan sambungan laju tinggi moden seperti yang terdapat pada port USB 3.0 atau kabel HDMI. Bagi situasi yang melibatkan ledakan tenaga yang lebih besar, varistor pelbagai lapisan digunakan. Ini memberikan perlindungan tambahan terhadap transien yang melebihi 20kV melalui mekanisme berbeza di mana elektron tersebar merentasi bahan oksida logam di dalam peranti. Disebabkan keupayaan ini, mereka kerap digunakan dalam melindungi talian bekalan kuasa dalam pelbagai persekitaran industri di mana keadaan melampau boleh menyebabkan kerosakan.

Ciri Voltan Pengapit, Masa Tindak Balas, dan TLP dalam Aplikasi Dunia Sebenar

Apabila melibatkan perlindungan terhadap descas elektrostatik, terdapat tiga perkara utama yang paling penting: berapa banyak voltan yang dikimpal, seberapa pantas peranti bertindak balas, dan apa yang berlaku apabila kita mengujinya dengan Pulse Garis Penghantaran (TLP). Ambil diod TVS yang diberi kadar kimpalan pada 5 volt - ini melindungi litar bersepadu sensitif kerana oksida get mereka cenderung rosak pada sekitar 10 volt. Untuk peranti RF seperti antena 5G, masa tindak balas di bawah setengah nanosaat sangat memberi kesan. Jika tidak, kerosakan kecil boleh terkumpul secara beransur-ansur tanpa disedari. Pengujian menggunakan kaedah TLP mengikut piawaian IEC 61000-4-2 menunjukkan dengan tepat bagaimana peranti-peranti ini gagal. Analisis plot arus melawan voltan membantu jurutera menentukan sama ada sesuatu itu tiba-tiba pulih atau kimpal secara perlahan. Apa yang ditemui pengeluar ialah diod TVS yang baik mengekalkan rintangan dinamiknya di bawah 10 ohm walaupun semasa denyutan kuat sehingga 30 amp. Ini sebenarnya lebih unggul berbanding penyelesaian berasaskan polimer apabila berurusan dengan isyarat frekuensi tinggi dalam elektronik moden.

Membandingkan Teknologi Penekanan ESD

| Komponen | Voltan Klem Biasa | Masa tindak balas | Arus Limpahan Maksimum | Kes Penggunaan |

|---|---|---|---|---|

| Diod TVS | 3–15V | <1 ns | 30A | Talian Data Berkelajuan Tinggi |

| Varistor Berbilang Lapisan | 20–600V | 5–50 ns | 70a | Rel Penghantaran Kuasa |

| Tiub Pelepasan Gas | 75–1000V | 100–500 ns | 20KA | Infrastruktur telecom |

Mengimbangi ketepatan pengapit penyekatan dan kapasiti lonjakan adalah penting–rekabentuk berlebihan meningkatkan kos, manakala perlindungan yang kurang berisiko menyebabkan kemasukan CMOS.

Mereka Bentuk Litar Perlindungan ESD yang Berkesan untuk Elektronik Moden

Untuk mereka bentuk litar perlindungan ESD yang baik, penting untuk meletakkan komponen penekanan seperti diod TVS betul-betul bersebelahan penyambung dan port input/output di mana lonjakan cenderung masuk terlebih dahulu sebelum sampai ke litar bersepadu yang sensitif. Voltan pemegun perlu ditetapkan sedikit di bawah paras yang akan merosakkan komponen yang dilindungi. Pada masa yang sama, mengekalkan kapasitans simpang yang rendah membantu mengekalkan kualiti isyarat bagi pemindahan data pantas yang kita lihat dalam antara muka moden. Laluan yang lebih pendek pada papan PCB mengurangkan induktans jejak yang menjadikan keseluruhan sistem lebih responsif apabila diperlukan. Ramai jurutera kini lebih memilih susunan perlindungan berperingkat kerana ia mengendalikan situasi sukar dengan jauh lebih baik berbanding penyelesaian titik tunggal. Mengikuti piawaian seperti ANSI/ESD S20.20-2021 memberi ketenangan fikiran kepada pengilang kerana mengetahui produk mereka mampu menahan kegagalan mengejut serta kerosakan perlahan yang berlaku dari semasa ke semasa. Ini menjadi lebih penting hari ini memandangkan cip terus mengecil, sehingga ke saiz nanometer di mana ia sebenarnya menjadi lebih rentan terhadap kerosakan elektrostatik. Pengujian pada peringkat sistem menggunakan kaedah TLP masih lagi penting, kerana keputusan makmal tidak sentiasa mencerminkan apa yang berlaku di lapangan dengan pelbagai kejadian statik yang tidak dijangka.

Persekitaran Kerja Selamat ESD: Dari Stesen Kerja hingga Pembungkusan

Lantai Penghakis Statik dan Pematuhan ISO 6360 dalam Pembuatan

Mencipta persekitaran selamat dari ESD bermula dengan bahan lantai yang sesuai seperti jubin EPDM yang diresap dengan sifat konduktif. Lantai-lantai ini mengekalkan rintangan permukaannya dalam julat 1 juta hingga 1 bilion ohm, membolehkan cas statik disebar secara selamat dan bukannya terkumpul. Menurut piawaian ISO 6360-5, kemudahan perlu menguji rintangan lantai dan sambungan pembumian secara berkala. Syarikat-syarikat yang mengikut garis panduan ini telah mencatatkan kejadian descas elektrostatik sebanyak kira-kira 75% lebih rendah berbanding mereka yang tidak mematuhinya, menurut penyelidikan dari ERAI pada tahun 2023. Sistem ini berfungsi dengan menghubungkan titik-titik pembumian antara lantai, permukaan kerja, dan pembumian bumi yang sebenar. Ini mencipta litar lengkap yang menghalang voltan daripada meningkat melebihi 100 volt, yang secara umumnya dianggap sebagai ambang keselamatan bagi litar bersepadu sensitif yang digunakan dalam pembuatan elektronik.

Beg Perlindungan Dua Lapisan dan Prinsip Sangkar Faraday untuk Penyimpanan Selamat

Beg perisai dua lapisan berfungsi berdasarkan konsep sangkar Faraday untuk melindungi komponen ketika disimpan atau dipindahkan. Lapisan luar mempunyai salutan logam yang menolak sebarang elektrik statik daripada sumber luar, manakala bahagian dalam yang diperbuat daripada plastik khas membantu menghilangkan cas yang terkumpul di dalam beg itu sendiri. Beg perlindungan ini mengurangkan paras tenaga elektrostatik sebanyak kira-kira 50 desibel, menghalang nyahcas melebihi voltan sekitar 8,000 mengikut piawaian IEC. Penutupan yang betul adalah sangat penting kerana jika tidak ditutup dengan sempurna, perlindungan akan berkurangan hampir 90 peratus. Apabila mengendalikan bahan sensitif seperti sensor CMOS, menyimpannya di dalam kabinet persekitaran terkawal dengan kelembapan di bawah tiga puluh peratus sangat membantu mencegah masalah tersembunyi pada masa hadapan. Memastikan perisai Faraday kekal utuh sepanjang penghantaran dan pengendalian adalah amat penting kerana hanya satu saat tanpa perlindungan yang mencukupi boleh merosakkan semua usaha lain dalam melindungi komponen bernilai tersebut.

Soalan Lazim

Apa itu Pelepasan Elektrostatik (ESD)?

Pelepasan elektrostatik (ESD) berlaku apabila terdapat aliran elektrik yang tiba-tiba antara dua objek bercas elektrik, sering kali menyebabkan kerosakan kepada elektronik yang sensitif.

Mengapa perlindungan ESD penting bagi elektronik?

Perlindungan ESD adalah penting kerana pelepasan elektrostatik boleh menyebabkan kegagalan yang teruk, kerosakan tersembunyi, dan perubahan parameter dalam komponen elektronik, yang membawa kepada jangka hayat yang lebih pendek dan kos baikan yang tinggi.

Bagaimanakah ESD merosakkan elektronik?

ESD boleh merosakkan oksida get dan mengaktifkan litar silikon kawalan parasit dalam IC CMOS, menyebabkan arus yang merosakkan peranti tersebut.

Apakah diod TVS?

Diod TVS adalah komponen perlindungan yang digunakan untuk mengalihkan arus berlebihan dan lonjakan voltan dari litar yang sensitif, mencegah kerosakan akibat pelepasan elektrostatik.

Apakah kandang Faraday, dan bagaimanakah ia melindungi elektronik?

Kandang Faraday adalah struktur yang melindungi kandungannya daripada medan elektrostatik dan elektromagnetik, kerap digunakan sebagai penyelesaian pembungkusan untuk menyimpan komponen elektronik dengan selamat.