Deall ESD: Sut mae Rhyddhau Trydolstatig yn Niweidio Electronig Sensitif

Ffiseg ESD: Torri Ocsid y Gât a Latch-Up yn ICau CMOS

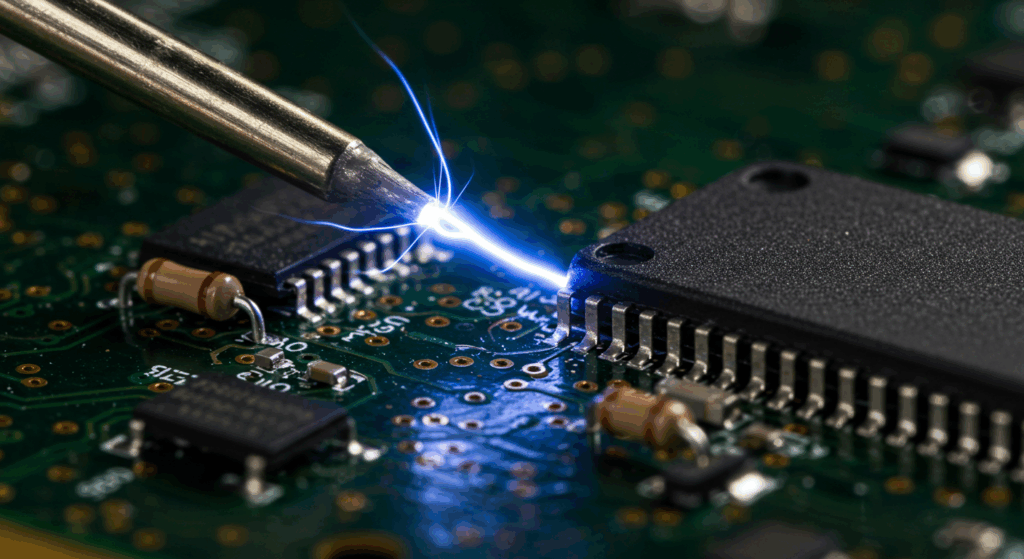

Mae ESD yn digwyd pan mae trydan statig yn grwm ac yna'n neidio rhwng gwrthrychau sydd â thâl trydanol gwahanol. Beth sy'n ei wneud yn beryglus? Wel, mae'r cyfluthro foltedd sydyn hynny'n mesur yn nifer fil o folt, ond ni allwn weld nhw o gwbl. Ar gyfer chipiau CMOS, mae'r ynni hwn yn mynd ar ôl y pwyntiau haeddef cyntaf. Mae tylwyr foltedd uchel yn taro trwy'r haenau ocsid gat wedyn, sy'n ladd y trawsnewyddion yn uniongyrchol. Mae problem arall hefyd. Gall y diodeau adolygu siliciom barasytig rhwystredig sydd wedi'u cuddio yn y substrat chip gael eu gweithredu yn ystod digwyd ESD. Pan mae hyn yn digwyd, maen nhw'n creu lwybrau â chynhwysiant isel sy'n gadael i gerdiant difroddus llifo'n rhydd, weithiau'n cyrraedd hyd at sawl amper o bŵer. Mae cylchoedd integredig modern yn cael eu lleihau yn eu maint ac yn gweithio ar folteddau llawer is, i tua 1.2 folt mewn rhai achosion. Hyd yn oed rhywbeth mor fach â 100 folt, sydd bell lawr o dan y lefelau gall ein synsau eu canfod, gall ddinistrio chip yn llwyr. Mae modelau thermol yn dangos bod tylwyr cyrhaeddi byr dros 10 amper yn gallu ymddifadu'r cysylltiadau bach tu mewn i chip mewn llai na hanner biliwnfed o eiliad. Dyna pam bod amddiffyniad ESD addas yn rhaid bellach, nid dim ond syniad da, er mwyn atal electronig rhag methu'n ddifrifol.

Mathau o Ddamwain ESD: Ffawdrefn, Cudd a Methiant Paramedrig

Mae dadgae droesgafnodol yn ymddangos o fewn tri ffyrdd prifol wrth ei gymharu â niweidio trydaneg, ac mae'r problemau hyn yn cael eu cryfhau wrth i ddyfeisiau oedreddu. Y fath fuddugoliaeth fwyaf amlwg yw methiant catastraffig, ble mae'r ddyfais yn 'marw' yn syth oherwydd niweidrwydd weladwy fel rhanau wedi'u losgu neu lwybrau metel wedi'u haddfu, sydd yn weladwy tra phrofi. Yna mae 'na niwed cudd, sy'n llawer fwy dalterus. Mae tollau bach yn ffurfio mewn cysylltiadau semiconductor neu mae ocsidion y dorfa yn chwalu dros amser. Gallai'r materion hyn groesi profion cychwynnol ond yn y pen draw achosi i gynnyrch fethre yn gynnar ar faes. Mae adroddiadau diwydiant yn awgrymu bod bwrddau gyda niweidrwydd ESD cudd yn aml yn para dim ond 40 i 60 y cant o'r hyn y dylent. Mae methiannau paramedrig yn gategori arall, lle mae priodweddau trydanol yn newid heb fod yn fethiant llwyr. Meddyliwch am guradr leci yn cynyddu neu lefelau voltedd yn symud o allan o barometrau, sy'n rhwbio â thimeio a chyfrannedd arwyddion. Mae costio tua £5,000 i bob un i ddatrys methiannau catastraffig yn ôl ymchwil Ponemon o 2023, tra bod delio â materion cudd yn defnyddio arian warant, gan ei bod mor amser ac ymdrech i ddarganfod beth aeth o'i le. Mae amddiffyniad da rhag ESD angen amddiffyn pob un o'r senarios hyn trwy lawer o haenau o amddiffyniad drwy gydol y broses gynhyrchu.

| Math o Fethiant | Ffenestr Darganfod | Effaith Ariannol | Dangosiad Corfforol |

|---|---|---|---|

| Anrhydeddus | Ymmidus | Sgript + atal producim | Cysylltiadau hylif wedi'u torri, toriad ocsid |

| Cudd | Wythnosau i fisoedd | Hawliau warant + adferion | Dadfa chwyldro addas |

| Paramedrig | Gwanwynnau profi | Colled ym mynydd a gweithredu eto | Golchiad uwch, drylliad amseru |

Cydresymau Diogelu Craidd ESD a Datrysiadau Cydrannau

Sut mae Drysiau TVS a Chynhalwyr Taro yn Dibynnu Arnerji ESD

Mae diaffodau TVS yn gweithredu fel y ffordd gyntaf o amddiffyn rhag tarwdaoâu trydan drwy gyfeirio cyfred ychwanegol i ffwrdd oddi ar gylchoedd sensitif pan fo rhywbeth fel tarell statig o 8kV yn digwydd o brofiad model corff dynol. Beth sy'n gwneud y cydrannau hyn yn effeithiol yw eu gallu i dalu'r buwstiau mewn iachau oherwydd broses o dorri lawr anawel isel. Gallant ddod â tharwdaoâu hyd at 30 amp tan eu hanfon yn ddiogel i dir, ac yn y pen draw cadw'r cylchoedd i lawr yn gweithredu o fewn terfynau derbynadwy. Mae amserau ymateb hefyd yn anhygoel o gyflym, gan amlwg islaw un nanoeiliad, sy'n esbonio pam maen nhw'n gweithio mor wych ag cysylltiadau uchelgyflym modern fel y rheini a gawn eu canfod mewn porthau USB 3.0 neu gabliau HDMI. Ar gyfer sefyllfaoedd sy'n cynnwys buwstiau egni hyd yn fympa, mae amrywiwrion sawl haen yn dod i chwarae. Mae'r rhain yn cynnig amddiffyniad ychwanegol rhag trowydd annrosglwyddo sy'n fwy na 20kV trwy wahanol ddyfodiaeth ble mae electronau'n anelu ar draws deunydd ocsid metel o fewn y ddyfais. Oherwydd y gallu hwn, maen nhw'n cael eu defnyddio'n gyffredin i amddiffyn llinellau cyflenwi pŵer o fewn amryw o osodiadau diwydol lle gallai amodau eithaf eraill ei achosi niwed.

Cymeradwyo'r Foltedd, Amser Ymateb, a Nodweddion TLP mewn Aplicau Bywyd-Real

Pan ddaw i amddiffyn rhag disgyblaeth electrostatig, mae yna dri pheth sy'n bwysig fwyaf: faint o foltedd sy'n cael ei glans, pa mor gyflym y mae'r ddyfais yn ymateb, a beth sy'n digwydd pan fyddwn yn ei brofi gyda Pulsau llinell drosglwyddo (TLP). Cymerwch diod TVS wedi'i reitllio ar 5 volts ar gyfer clamp - mae hyn yn cadw'r cylchlyfrau integredig sensitif hynny'n ddiogel gan fod eu ocsid porth yn tueddu i dorri tua 10 volts. Ar gyfer pethau RF fel antennau 5G, mae cael amseroedd ymateb o dan hanner nanodydd yn gwneud gwahaniaeth. Fel arall, gall darnau bach o ddifrod adeiladu dros amser heb i neb sylwi. Mae profi gyda dulliau TLP yn unol â safonau IEC 61000-4-2 yn dangos i ni sut mae'r dyfeisiau hyn yn methu yn union. Mae edrych ar graffiau cornel yn erbyn foltedd yn helpu peirianwyr i ddweud a yw rhywbeth yn cnappio yn sydyn neu'n clampiau'n ofalus. Mae gwneuthurwyr yn canfod bod diodau TVS da yn cadw eu gwrthsefyll dynamig o dan 10 ohm hyd yn oed yn ystod impulsau 30 amp mawr. Mae hyn mewn gwirionedd yn guro atebion ar sail polymer wrth ddelio â signalau amlaf amlder mewn electroneg fodern.

Cymharu Technolegau Crybwyll ESD

| Aelod | Voltedd Glampio Tipynol | Amser ymateb | Cronfa Chwyldro Uchaf | Casgliad Defnydd |

|---|---|---|---|---|

| Diod TVS | 3–15V | <1 ns | 30A | Llinellau Data Cyflym |

| Amrywstadwr Aml-lefel | 20–600V | 5–50 ns | 70A | Sylfaen Pŵer |

| Teibl gwasgarth nwy | 75–1000V | hyd at 500 ns | 20KA | Infrastrwyduredd telecom |

Mae'n hanfodol i gael taclu cydbwysedig rhwng manyleb a chynhwysedd tarfu – mae rhy fwy na gofynion yn cynyddu'r cost, tra bod dan-ddiogelu yn cynyddu'r risg o gamdriniaeth CMOS.

Dylunio Sgriaus Diogelu ESD effeithiol ar gyfer Electronig Fodern

I ddylunio cylchoedd amddiffyn ESD da, mae'n bwysig gosod y gydrannau crymeiedig hyn fel diwodiad TVS yn union nesaf i gysylltwyddion a phorthiadau mewnbwn/allbwn ble mae tandaluon yn mynd i fewn yn gyntaf cyn cyrraedd y chwyldroadau integredig sensitif. Mae angen gosod y foltedd clipio i'r islawr beth fyddai'n niweidio'r gydrannau sydd dan amddiffyn. Yn yr un man, mae cadw hydlyddiant cymal isel yn helpu i gynnal ansawdd arwyddion ar gyfer y trosglwyddo data cyflym rydym yn eu gweld yn rhyngwynebau modern. Mae lwybrau byrach ar bwrdd PCB yn lleihau hydlyddiant olwyn sy'n gwneud i'r system gyfan ymateb well pan fo angen. Mae llawer o beiriannwyr yn dewis setiau amddiffyn sawl cyfnod nawr oherwydd eu bod yn llawso o lefelau anodd yn well na datrysiadau pwynt sengl. Mae dilynwch safonau fel ANSI/ESD S20.20-2021 yn rhoi meddwl trawiadol i gynhyrchwyr gan wybod eu bod yn gallu gwarantu eu cynnyrch yn erbyn methiannau sydyn a chwear yn araf dros amser. Mae hyn yn fwy pwysig heddiw oherwydd bod sips yn cael eu lleihau i fathau bytach, i faint nanometrau ble mae'u synhyrdeb i niwed trydanstatig yn cynyddu. Mae profi ar lefel y system gyda dulliau TLP yn hanfodol dal, er bod canlyniadau labordy yn aml yn anghydweddu â'r hyn sy'n digwydd yn y maes gyda llawer o ddigwyddiadau statig annisgwyl.

Amgylchedd Gwaith DDiogel ESD: O Farsnoedd Gwaith i Bacio

Gwreiddiau Statig-Diffusol a Chymeradwyaeth ISO 6360 yn y Manwerthu

Dechrau creu amgylchedd diogel ESD yw defnyddio deunyddiau llawr priodol fel teils EPDM sydd wedi'u hamlinellu â phriodoleddau cynhwysol. Mae'r llawr hwn yn cadw eu gwrthiant arwyneb o fewn ystod o 1 miliwn i 1 biliwn ohm, gan ganiatáu i gostau statig ddiflannu'n ddiogel yn hytrach na chasglu. Yn ôl safon ISO 6360-5, mae angen i gyfluniadau brosesu eu gwrthiant llawr a'u cysylltiadau grounding yn rheolaidd. Yn ôl ymchwil gan ERAI yn 2023, mae cwmni sy'n dilyn y canllawiau hyn wedi gweld tua 75% llai o ddigwyddiadau datrysiad electrostatig na rhai nad ydyn nhw'n cydymffurfio. Mae'r system yn gweithio trwy gysylltu pwyntiau grounding rhwng y llawr, wynebau gwaith, a thir gwirioneddol. Mae hyn yn creu cylched llawn sy'n atal voltedd rhag codi uwchben 100 folt, sydd fel arfer yn cael ei ystyried yn derfyn diogelwch ar gyfer cylchoedd integredig sensitif a ddefnyddir mewn manwerthu trydan.

Cilod Sgio Ddwy Haen a Chynlluniau Cages Faraday ar gyfer Storio'n Ddiogel

Mae ffoniau diogelu â dwy haen yn gweithio yn seiliedig ar gysyniadau carchar Faraday i gadw cydrannau'n saff pan gaiff eu storio neu eu symud. Mae'r haen allanol yn cynnwys grich metel sy'n gwrthsefyll unrhyw yrhaeddiad statig o ffynonellau allanol, tra bod y rhan fewnol wnaethir o ddur rhwystrol arbennig yn helpu cael gwared ar yrhaeddiadau mewnol o fewn y ffôn ei hun. Mae'r ffoniau diogelu hyn yn lleihau lefelau enerji electrostatig erbyn tua 50 decibel, gan atal yrhaeddiadau dros fras am 8,000 volt yn ôl safonau IEC. Mae cael y sêl yn iawn yn bwysig iawn yn wirionedd, gan os nad yw wedi'i gau'n gywir, mae'r diogelu'n gostwng gan bron 90 y cant. Pan ddynodir eitemau sensitif fel senwyddion CMOS, mae'u rhoi mewn cabinetiau amgylchedd rheolaidd ble mae lefel y gochrau yn aros dan degymau tri chant yn helpu i atal problemau cudd yn nes ymlaen. Mae cadw'r sgyld Faraday yn intact trwy gydol anfon a llawdrochi'n hanfodol iawn, gan un eiliad heb amddiffyn addas yn gall dadwneud popeth arall a wnaed i amddiffyn y rannau gwerthfawr hynny.

Cwestiynau Cyffredin

Beth yw Disgyniad Electrostatig (ESD)?

Mae dadgae drwst electrostatig (ESD) yn digwyd pan fo llif sudden o ddrudw yn digwyd rhwng dau wrthrych wedi'u masnachu'n drudw, a ddynod yn aml achosi damwain i electronig sensitif.

Pam mae amddiffyn rhag ESD yn bwysig ar gyfer trydarwyr?

Mae amddiffyniad ESD yn hanfodol oherwydd y gall dadgaed drwst electrostatig achosi methiannau catastraffig, damwain cudd, a newidiadau paramedrig mewn cydrannau electronig, gan arwain at fywyd hydrist byrach a chostau adrefu uchel.

Sut mae ESD yn niweidio electronig?

Gall ESD dorri ocsidau'r gatel a gweithredu adlewyrlydd siliciwn rhynggartrefol mewn ICau CMOS, gan achosi cyrrentau difrolyd sy'n niweidio'r ddyfais.

Beth yw deodiaid TVS?

Mae diwodau TVS yn gydrannau amddiffyniad a ddefnyddir i ddodrefi cyrrent a thrylediadau foltedd ychwanegol i ffwrdd o gynulliaid trydanol gref, ac yn atal damwain gan ddisgyniad electrostatig.

Beth yw cestyll Faraday, a sut mae'n amddiffyn electronig?

Mae cestyll Faraday yn strwythur sy'n amddiffyn y cynnwys o fewnno rhag meysydd statig a electromagnetig, a ddefnyddir yn aml fel datrysiad pecynnu ar gyfer storio cydrannau electronig yn saff.