فهم التفريغ الكهروستاتيكي: كيف يُحدث التفريغ الكهروستاتيكي أضرارًا في الإلكترونيات الحساسة

فيزياء التفريغ الكهروستاتيكي: تمزق طبقة الأكسيد في البوابة وظاهرة القفل (Latch-Up) في الدوائر المتكاملة CMOS

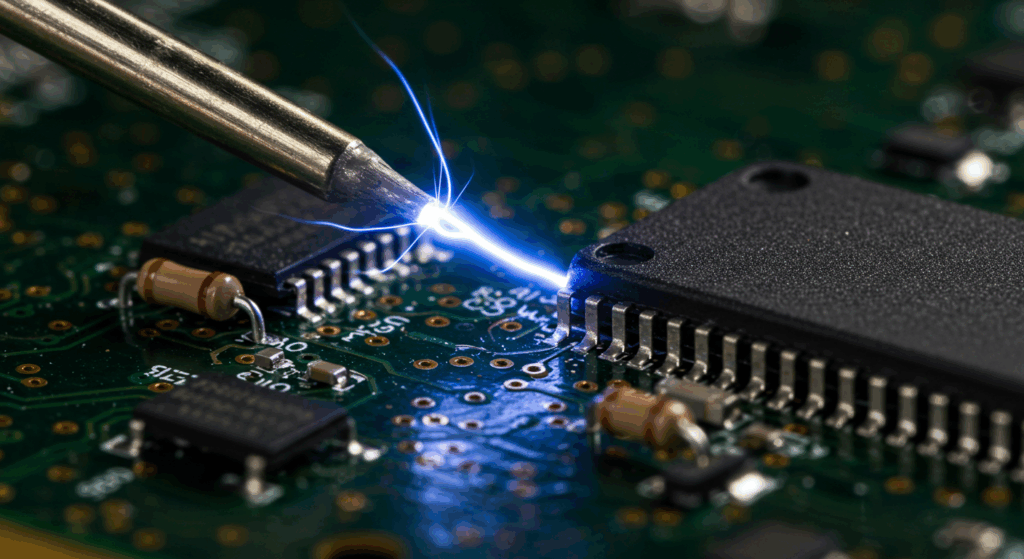

تحدث تفريغ الكهرباء الساكنة (ESD) عندما تتراكم الكهرباء الساكنة ثم تقفز بين جسمين لهما شحنات كهربائية مختلفة. ما الذي يجعلها خطرة؟ حسنًا، فإن هذه الزيادات المفاجئة في الجهد تُقاس بالآلاف، ولكننا لا نستطيع رؤيتها على الإطلاق. بالنسبة لشرائح CMOS، فإن هذه الطاقة تستهدف أولًا النقاط الأضعف. وتدمّر قمم الجهد العالية طبقات أكسيد البوابة الرفيعة جدًا، مما يؤدي إلى تدمير الترانزستورات فورًا. وهناك مشكلة أخرى أيضًا. فقد تُفعَّل أجهزة التقويم السيليكونية المتسللة المزعجة المختبئة في قاعدة الشريحة أثناء حدث تفريغ كهربائي ساكن. وعندما يحدث ذلك، فإنها تُنشئ مسارات منخفضة المقاومة تسمح بمرور تيارات مدمرة بحرية، تصل أحيانًا إلى عدة أمبيرات من الطاقة. أصبحت الدوائر المتكاملة الحديثة أصغر حجمًا وتعمل بجهود أقل بكثير الآن، تصل إلى حوالي 1.2 فولت في بعض الحالات. حتى شيء صغير مثل 100 فولت، وهو أقل بكثير من الحد الذي يمكن لحواسنا اكتشافه، قد يؤدي إلى تدمير الشريحة تمامًا. تُظهر النماذج الحرارية أن قفزات التيار القصيرة التي تتجاوز 10 أمبير يمكن أن تذيب فعليًا الوصلات الصغيرة داخل الشريحة في أقل من نصف مليار جزء من الثانية. ولهذا السبب لم يعد الحماية المناسبة من تفريغ الكهرباء الساكنة مجرد إضافة جيدة، بل أصبحت ضرورية تمامًا لمنع الأعطال الكارثية في الإلكترونيات.

أنواع تلف ESD: الفشل الكارثي، الكامن، والفساد المعلمي

تظهر التفريغات الكهروستاتيكية بثلاث طرق رئيسية عند إتلاف الإلكترونيات، وتتفاقم هذه المشكلات تدريجيًا مع تقدم أجهزة التشغيل عمرًا. النوع الأكثر وضوحًا هو الفشل الكارثي، حيث يتوقف الجهاز عن العمل فورًا بسبب أضرار مرئية مثل أجزاء محترقة أو مسارات معدنية منصهرة يمكن رؤيتها أثناء الاختبار. ثم هناك الضرر الكامن الذي يكون أكثر خداعًا بكثير. تتكون ثقوب صغيرة في وصلات أشباه الموصلات أو يحدث تدهور في أكاسيد البوابة مع مرور الوقت. قد تجتاز هذه المشكلات الاختبارات الأولية، ولكنها في النهاية تؤدي إلى فشل المنتجات مبكرًا في الاستخدام الميداني. تشير تقارير الصناعة إلى أن اللوحات التي تعاني من أضرار كامنة ناتجة عن التفريغ الكهروستاتيكي غالبًا ما تدوم فقط من 40 إلى 60 بالمئة من المدة المقررة لها. وفئة أخرى هي حالات الفشل المعاملية، حيث تتغير الخصائص الكهربائية دون حدوث فشل كامل. على سبيل المثال، زيادة التسريب الكهربائي أو انحراف مستويات الجهد عن المواصفات، مما يخل بالتوقيت وجودة الإشارة. وفقًا لبحث بونيمون لعام 2023، فإن تكلفة إصلاح حالات الفشل الكارثي تبلغ حوالي 5000 دولار لكل حالة، في حين تستنزف المشكلات الكامنة ميزانيات الضمان لأن تحديد سبب الخلل يستغرق الكثير من الوقت والجهد. تتطلب الحماية الجيدة من التفريغ الكهروستاتيكي تغطية جميع هذه السيناريوهات بطبقات متعددة من الدفاع على امتداد عملية التصنيع.

| نوع الفشل | نافذة الكشف | الأثر المالي | التجلّي المادي |

|---|---|---|---|

| كوارثي | فوري | خردة + توقف الإنتاج | وصلات متصلة مصهورة، تمزق الأكسيد |

| كامن | أسابيع إلى أشهر | مطالبات الضمان + الاستدعاءات | تدهور الوصلة التدريجي |

| باراميتري | أثناء الاختبار | فقدان العائد + إعادة العمل | تسرب مرتفع، انحراف في التوقيت |

آليات الحماية الأساسية من التفريغ الكهروستاتيكي والحلول المكونة

كيف تقوم دايودات TVS ومقاومات التفريغ بتحويل طاقة التفريغ الكهروستاتيكي

تعمل دايودات TVS كآلية دفاع أولية ضد الاندفاعات الكهربائية من خلال تحويل التيار الزائد بعيدًا عن الدوائر الحساسة عندما يحدث تفريغ ساكن مثل 8 كيلو فولت من اختبار نموذج جسم الإنسان. ما يجعل هذه المكونات فعّالة هو قدرتها على تثبيت قفزات الجهد بسرعة بفضل عملية تُعرف باسم انهيار الانفجار ذو المعاوقة المنخفضة. ويمكنها تحمل دفعات تصل إلى 30 أمبير قبل إرسالها بأمان إلى الأرض، وفي الوقت نفسه تبقي الدوائر الواقعة في الأسفل تعمل ضمن الحدود المقبولة. كما أن أزمنة الاستجابة سريعة جدًا، وغالبًا ما تكون أقل من نانوثانية واحدة، مما يفسر سبب كفاءتها العالية مع الاتصالات الحديثة عالية السرعة مثل الموجودة في منافذ USB 3.0 أو كابلات HDMI. وفي الحالات التي تنطوي على دفعات طاقة أكبر، تُستخدم مقاومات متعددة الطبقات. وتوفر هذه المقاومات حماية إضافية ضد الظواهر العابرة التي تتجاوز 20 كيلو فولت من خلال آلية مختلفة، حيث تنتشر الإلكترونات عبر مواد أكاسيد المعادن داخل الجهاز. ونتيجة لهذه القدرة، تُستخدم بشكل شائع في حماية خطوط إمداد الطاقة ضمن مختلف البيئات الصناعية، حيث قد تؤدي الظروف القصوى بخلاف ذلك إلى تلف الأجهزة.

جهد التثبيت، وقت الاستجابة، وتمييز TLP في التطبيقات الواقعية

عندما يتعلق الأمر بالحماية من التفريغ الكهروستاتيكي، فهناك ثلاث أمور أساسية هي الأهم: كمية الفولتية التي يتم تثبيتها، وسرعة استجابة الجهاز، وما يحدث عندما نختبره باستخدام نبضات خط النقل (TLP). خذ على سبيل المثال ديود TVS مصنف بجهد تثبيت 5 فولت - وهذا يحافظ على الدوائر المتكاملة الحساسة آمنة، لأن أكاسيد البوابة الخاصة بها عادة ما تتلف عند حوالي 10 فولت. بالنسبة للإشارات الراديوية مثل هوائيات 5G، فإن تحقيق أزمنة استجابة أقل من نانوثانية واحدة يُحدث فرقًا كبيرًا. وإلا، يمكن أن تتراكم أضرار طفيفة بمرور الوقت دون أن يلاحظها أحد. تُظهر لنا اختبارات طريقة TLP وفقًا لمعايير IEC 61000-4-2 كيف يفشل هذه الأجهزة بالضبط. وتساعد دراسة منحنيات التيار مقابل الجهد المهندسين على التمييز بين ما إذا كان الفشل يحدث فجأة بشكل انعكاسي مفاجئ أو تدريجيًا بطريقة التثبيت اللطيف. ما تجده الشركات المصنعة هو أن ديودات TVS الجيدة تحافظ على مقاومتها الديناميكية أقل من 10 أوم حتى أثناء نبضات كهربائية كبيرة تصل إلى 30 أمبير. وهذا في الواقع يتفوق على الحلول القائمة على البوليمر عند التعامل مع الإشارات عالية التردد في الإلكترونيات الحديثة.

مقارنة تقنيات كبت التفريغ الكهروستاتيكي

| مكون | جهد التثبيت النموذجي | زمن الاستجابة | أقصى تيار زائد | حالة الاستخدام |

|---|---|---|---|---|

| ثنائي التلفزيون | 3–15V | <1 نانوثانية | 30 أمبير | خطوط بيانات عالية السرعة |

| مقاوم متعدد الطبقات | 20–600V | 5–50 نانوثانية | 70A | مسارات إمداد الطاقة |

| أنبوب تفريغ الغاز | 75–1000V | 100–500 نانوثانية | 20KA | البنية التحتية للاتصالات |

من الضروري موازنة دقة التثبيت مع سعة التيار الزائدة – فالتقنية المفرطة تزيد التكلفة، بينما عدم كفاية الحماية يعرّض الدوائر المنطقية (CMOS) لحالة القفل (latch-up).

تصميم دوائر حماية فعالة من التفريغ الكهروستاتيكي للإلكترونيات الحديثة

لتصميم دوائر حماية جيدة من التفريغ الكهروستاتيكي (ESD)، من المهم وضع مكونات العزل مثل ديودات TVS بالقرب من الموصلات ومنافذ الإدخال/الإخراج حيث تميل الاندفاعات إلى الدخول أولًا قبل الوصول إلى الدوائر المتكاملة الحساسة. يجب ضبط جهد القمع ليكون أعلى قليلاً من الجهد الذي قد يتلف المكونات المراد حمايتها. في الوقت نفسه، يساعد الحفاظ على انخفاض سعة الوصلة في الحفاظ على جودة الإشارة بالنسبة للنقل السريع للبيانات الموجود في الواجهات الحديثة. وتقلل المسارات الأقصر على لوحة الدوائر المطبوعة (PCB) من الحث الزائدي، مما يجعل النظام بأكمله يستجيب بشكل أفضل عند الحاجة. يفضل العديد من المهندسين الآن استخدام ترتيبات الحماية متعددة المراحل لأنها تعالج المواقف الصعبة بشكل أفضل بكثير من الحلول ذات النقطة الواحدة. واتباع المعايير مثل ANSI/ESD S20.20-2021 يمنح المصنّعين طمأنينة بقدرة منتجاتهم على تحمل كل من الأعطال المفاجئة والتآكل البطيء مع مرور الوقت. ويكتسب هذا أهمية أكبر اليوم نظرًا لاستمرار تصغير الشرائح إلكترونيًا حتى أبعاد النانومتر، حيث تصبح أكثر عرضة للتلف الناتج عن الكهرباء الساكنة. ولا يزال اختبار المستوى النظامي باستخدام أساليب TLP أمرًا بالغ الأهمية، لأن نتائج المختبر لا تعكس دائمًا ما يحدث فعليًا في البيئة الخارجية مع تنوع أحداث الكهرباء الساكنة غير المتوقعة.

بيئات العمل المحمية من التفريغ الكهربائي الساكن: من محطات العمل إلى التعبئة والتغليف

أرضيات مقاومة للكهرباء الساكنة والامتثال لمعيار ISO 6360 في التصنيع

يبدأ إنشاء بيئة آمنة من التفريغ الكهروستاتيكي (ESD) باستخدام مواد أرضيات مناسبة مثل بلاط EPDM المُحمّل بخصائص توصيلية. تحافظ هذه الأرضيات على مقاومتها السطحية ضمن النطاق بين مليون وأحدى البليون أوم، مما يسمح بالتفريغ الآمن للشحنات الكهروستاتيكية بدلاً من تراكمها. وفقًا للمواصفات القياسية ISO 6360-5، يجب على المرافق اختبار مقاومة الأرضية ووصلات التأريض بشكل دوري. وقد أظهرت الأبحاث الصادرة عن ERAI في عام 2023 أن الشركات التي تتبع هذه الإرشادات تسجّل انخفاضًا بنسبة 75٪ تقريبًا في حوادث التفريغ الكهروستاتيكي مقارنةً بتلك التي لا تمتثل لها. يعمل النظام من خلال ربط نقاط التأريض بين الأرضية وأسطح العمل والأرض الفعلية، ما يكوّن دائرة كهربائية كاملة تمنع تراكم الجهد بما يتجاوز 100 فولت، وهي عتبة الأمان المقبولة عمومًا بالنسبة للدوائر المتكاملة الحساسة المستخدمة في تصنيع الإلكترونيات.

أكياس الحماية ثنائية الطبقة ومبدأ قفص فاراداي للتخزين الآمن

تعمل أكياس التدريع ذات الطبقتين على أساس مفهوم قفص فاراداي للحفاظ على المكونات آمنة أثناء التخزين أو النقل. تحتوي الطبقة الخارجية على طلاء معدني يصد الكهرباء الساكنة القادمة من المصادر الخارجية، في حين أن الجزء الداخلي المصنوع من بلاستيك خاص يساعد على التخلص من الشحنات المتراكمة داخل الكيس نفسه. تقلل هذه الأكياس الواقية مستويات الطاقة الكهروستاتيكية بنحو 50 ديسيبل، وتحvented التفريغ عند حوالي 8000 فولت وفقًا لمعايير IEC. إن إغلاق اللحام بشكل صحيح أمر بالغ الأهمية، لأنه إذا لم يتم إغلاق الكيس بشكل جيد، فإن مستوى الحماية ينخفض بنسبة تقارب 90 بالمئة. وعند التعامل مع مكونات حساسة مثل مستشعرات CMOS، فإن وضعها في خزائن بيئة محكومة تبقى فيها الرطوبة أقل من ثلاثين بالمئة يُعدّ خطوة فعالة لمنع المشكلات الخفية لاحقًا. ويظل الحفاظ على سلامة درع فاراداي طوال مراحل الشحن والتعامل أمرًا بالغ الأهمية، إذ يمكن لحظة واحدة فقط بدون حماية كافية أن تُبطل كل الإجراءات الأخرى المتخذة لحماية تلك المكونات القيّمة.

الأسئلة الشائعة

ما هو التفريغ الكهروستاتيكي (ESD)؟

تحدث التفريغ الكهروستاتيكي (ESD) عندما يكون هناك تدفق مفاجئ للتيار الكهربائي بين جسمين مشحونين كهربائيًا، وغالبًا ما يتسبب في تلف الإلكترونيات الحساسة.

لماذا تعتبر حماية ESD مهمة للإلكترونيات؟

تُعد حماية التفريغ الكهروستاتيكي ضرورية لأن التفريغ الكهروستاتيكي يمكن أن يتسبب في فشل كارثي، أو تلف كامن، أو تغيرات بارامترية في المكونات الإلكترونية، مما يؤدي إلى تقصير عمر الجهاز وزيادة تكاليف الإصلاح.

كيف يتلف التفريغ الكهروستاتيكي الإلكترونيات؟

يمكن أن يتسبب التفريغ الكهروستاتيكي في تمزق أكاسيد البوابة وتفعيل مقومات السيليكون التحكمية المتسللة في الدوائر المتكاملة من نوع CMOS، ما يولد تيارات مدمرة تضر الجهاز.

ما هي ديودات TVS؟

تُعد دايودات TVS مكونات واقية تُستخدم لإعادة توجيه التيارات الزائدة والاندفاعات الكهربائية بعيدًا عن الدوائر الحساسة، ومنع الضرر الناتج عن التفريغ الكهروستاتيكي.

ما هي قفص فاراداي، وكيف يحمي الإلكترونيات؟

قفص فاراداي هو هيكل يحمي محتوياته من المجالات الكهروستاتيكية والكهرومغناطيسية، ويُستخدم غالبًا كحل تغليف لتخزين المكونات الإلكترونية بأمان.

جدول المحتويات

- فهم التفريغ الكهروستاتيكي: كيف يُحدث التفريغ الكهروستاتيكي أضرارًا في الإلكترونيات الحساسة

- آليات الحماية الأساسية من التفريغ الكهروستاتيكي والحلول المكونة

- تصميم دوائر حماية فعالة من التفريغ الكهروستاتيكي للإلكترونيات الحديثة

- بيئات العمل المحمية من التفريغ الكهربائي الساكن: من محطات العمل إلى التعبئة والتغليف

- الأسئلة الشائعة