Mereka bentuk secara efektif Litar perlindungan ESD ialah suatu disiplin kejuruteraan kritikal yang meluas jauh di luar sekadar memasang penekan voltan sementara (TVS) pada skematik. Ia merupakan suatu latihan holistik dalam pengurangan risiko, pemeliharaan integriti isyarat, dan jaminan pematuhan. Objektif utamanya ialah mengalihkan arus besar akibat peristiwa Pelepasan Elektrostatik (ESD)—yang boleh mencapai beberapa puluh amp dalam masa kurang daripada satu nanosaat—jauh dari litar bersepadu (IC) yang sensitif, dengan demikian mengekalkan voltan merentasi IC-IC tersebut pada tahap yang selamat . Kegagalan mencapai objektif ini boleh menyebabkan kegagalan teruk serta-merta atau kerosakan laten yang muncul sebagai pulangan awal di medan, seterusnya menghakis kebolehpercayaan produk dan reputasi jenama.

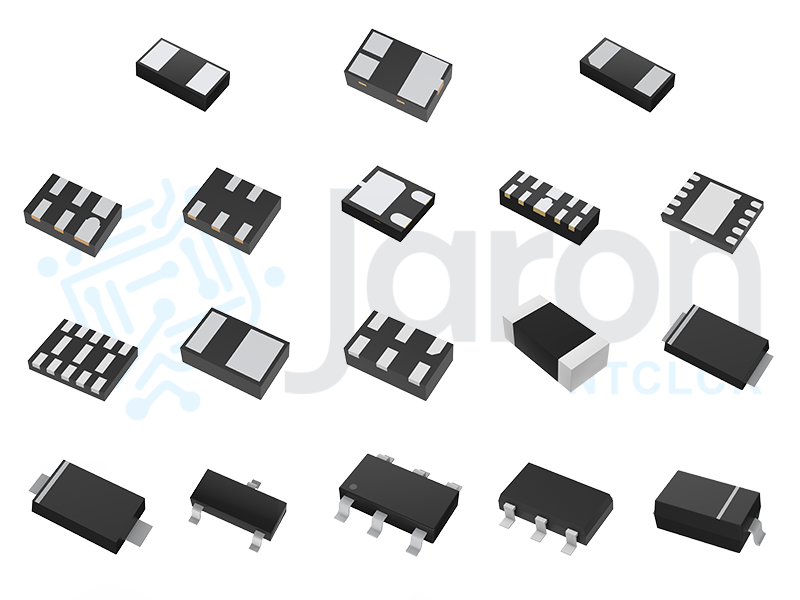

Landasan utama bagi suatu Litar perlindungan ESD ialah pemilihan teliti peranti perlindungan, yang dipandu oleh hierarki parameter elektrik. Pertama, Voltan Operasi Peranti (VRWM) mesti lebih tinggi daripada voltan operasi normal maksimum talian yang dilindunginya untuk mengelakkan arus bocor semasa operasi biasa kedua, dan yang paling kritikal, Voltan Pengapitannya (VC) di bawah arus surja yang dijangka mesti lebih rendah daripada kadar voltan maksimum mutlak bagi IC yang dilindungi. Sebagai contoh, melindungi pin GPIO mikroponroler yang diberi kadar 10 V memerlukan diod TVS dengan VC yang jauh di bawah 10 V pada arus surja yang berkaitan ketiga, kapasitans parasitik (Cj) peranti menjadi pemboleh ubah pengekang utama bagi antara muka data berkelajuan tinggi. Pelindung dengan kapasitans beberapa ratus pikofarad, walaupun sesuai untuk rel kuasa, akan mengurangkan isyarat secara ketara pada talian USB 3.0 (5 Gbps) atau HDMI. Bagi aplikasi ini, pelindung ESD khas dengan kapasitans di bawah 1 pF atau malah 0.5 pF adalah wajib untuk mengelakkan pengubahan bentuk isyarat .

Persekitaran aplikasi menentukan ketegasan rekabentuk. Di elektronik Automotif , An Litar perlindungan ESD mesti melindungi terhadap transien unik yang dinyatakan dalam ISO 7637-2 dan ISO 16750-2, seperti peristiwa ‘load dump’ . Komponen mesti memenuhi piawaian AEC-Q101 dan beroperasi secara boleh percaya dalam julat suhu dari −40°C hingga +125°C (atau lebih luas) . Melindungi bus CAN, sebagai contoh, sering memerlukan diod TVS dwiarah dengan voltan VRWM sebanyak 24 V untuk sistem 12 V bagi mengendalikan lonjakan voltan, dan penempatannya mesti berdekatan langsung dengan penyambung untuk meminimumkan induktans jejak parasitik yang boleh merosakkan prestasi .

Untuk peralatan Industri , teh Litar perlindungan ESD kerap perlu mengendalikan gangguan elektrik yang lebih luas seperti Transien Elektrik Pantas (EFT) mengikut IEC 61000-4-4, selain daripada ESD . Melindungi port komunikasi RS-485 dalam persekitaran kilang mungkin melibatkan peranti yang diperkadangkan untuk ketahanan ESD yang tinggi (contohnya ±30 kV) dan arus puncak (Ipp) yang besar bagi memastikan integriti komunikasi di tengah-tengah gangguan elektrik .

Akhirnya, satu kejayaan Litar perlindungan ESD ialah keseimbangan antara pemilihan komponen yang betul, susun atur PCB yang bijak (laluan pendek dan berinduktans rendah ke tanah), serta pengesahan melalui ujian kesesuaian (contohnya, IEC 61000-4-2 Tahap 4). Mengatasi kerumitan ini memerlukan akses kepada komponen yang sesuai serta sokongan pakar. Untuk bantuan pakar dalam memilih peranti perlindungan yang paling optimum bagi aplikasi kenderaan automotif, industri, atau antara muka kelajuan tinggi anda, serta untuk mendapatkan sebut harga yang kompetitif bagi senarai bahan anda, sila hubungi pasukan jualan teknikal kami. Kami memanfaatkan akses kami kepada pengilang terkemuka dan kepakaran rantaian bekalan untuk menyampaikan penyelesaian perlindungan ESD yang lengkap.